Fan-out wafer level packaging (FOWLP) technology is an increasingly popular solution for obtaining high levels of device integration with a greater number of I/O contacts, at a lower cost. With FOWLP today we have the ability to embed heterogeneous devices including baseband processors, RF transceivers, and power management ICs in mold wafers, thereby enabling the latest generation of ultra-thin wearables and mobile wireless devices. With continued line and space reductions, FOWLP has the potential to accommodate higher performing devices including memory and application processors, positioning FOWLP to extend into new markets including automotive and medical applications and beyond.

In all FOWLP schemes, such as InFO (TSMC), SWIFT/SLIM (Amkor), eWLB (STATS ChipPAC, ASE, NANIUM) and many others, singulated dies are embedded in epoxy mold compound (EMC). While EMC is a cost-effective material, it readily absorbs moisture, as do the polymer dielectrics used to electrically isolate adjacent metal interconnect lines.

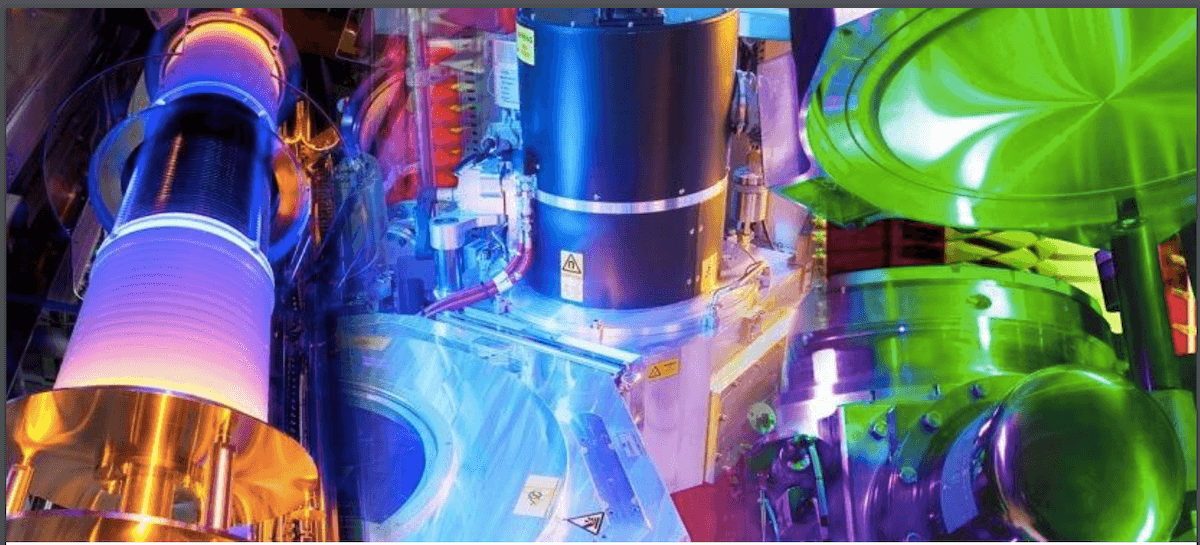

At the recent IWLPC 2016 conference, Chris Jones, Director – PVD Product Management, from SPTS Technologies presented a paper that defined some of these process challenges facing manufacturers when depositing metal layers onto mold wafers for high-density fan-out wafer level packaging (FOWLP) applications. The paper illustrated how various hardware and process modifications had been implemented to address the issues associated with working with mold wafers and still deliver the cost benefits of FOWLP schemes. Methods to deal with particles, moisture contamination, handling warped wafers, and controlling plasma stability in high-volume manufacturing was presented. These developments included a multi-wafer degas solution which is already being used by many leading OSATs and foundries to increase wafer throughput when faced with long, low temperature degas requirements. Also included was the “SE-LTX”, a novel pre-clean etch module developed by SPTS, which incorporates in-situ pasting to improve adherence of carbon deposits onto the chamber parts (i.e. not falling onto the wafer) and thus increases the time between dedicated wafer passes by a factor of 10, resulting in less disruption to production.

Download the white paper.

Download the presentation.

This was presented as part of the 2016 International Wafer-level Packaging Conference, October 18-20, 2016