Eight years in the making, the IEEE Std 1838™-2019 Standard for Test Access Architecture for Three-Dimensional Stacked Integrated Circuits — or IEEE 1838, DfT for 3D IC, as it’s known in inner circles – was published on March 13, 2020. Simply put, this standard will allow stacked dies in 3D ICs to connect with test equipment. The timing couldn’t be better, as a variety of approaches for 2.5D and 3D stacking technologies are entering the mainstream and combine dies from different suppliers. A consistent, stack-level design-for-test (DfT) architecture will be essential to simplify in-line test processes and improve time-to-market.

(Photo: Christie’s Photographic Solutions)

I recently spoke with Erik Jan Marinissen, scientific director at imec, and Adam Cron, the principal engineer in the Design Group at Synopsys, both champions of this effort since its very beginnings, to get an inside look into developing IEEE 1838.

What is IEEE Std 1838?

Essentially, IEEE 1838 is a DfT standard for 3D ICs. It describes how to build an architecture that makes it possible, once multiple dies are stacked, to separately test the dies that possibly contain embedded cores, and 3D interconnects. This is particularly important with the plethora of different dies being produced by different manufacturers and is being stacked using a variety of approaches.

Marinissen says he first developed a 3D test architecture for imec back in 2010. It provided a foundation for IEEE 1838. “I hoped it could immediately serve as the standard,” he said. But working with other companies with different ideas and different architectures made it clear that writing the standard wouldn’t happen overnight. This was not a surprise to him, however, as this was not his first rodeo, so to speak.

“I also worked on IEEE 1500, a DfT standard for embedded cores, and that also took eight years. At the time, it was the longest development time for an IEEE DfT standard,” said Marinissen. “There was lots of debate around it, but it still was in time for the market. It was not my intention that this new standard for 3D-DfT, IEEE 1838, would again take eight years to complete. Everyone will applaud it finally being published.”

While JEDEC also develops test standards, all DfT standards fall under IEEE, such as IEEE Std 1149.1™-1990, DfT for printed circuit boards (PCBs), and IEEE Std 1500™-2005, DfT for systems-on-chip (SoC), explained Marinissen. This way, working groups can leverage the guidelines that apply to the new architectures, and build on them.

Consider that dies in a 3D stack have features similar to ICs on a PCB, as they are ICs in their own right. They also have features similar to embedded cores in an SoC. Even after stacking, not just the 3D interconnects between the stacked dies, but also the dies themselves should be testable.

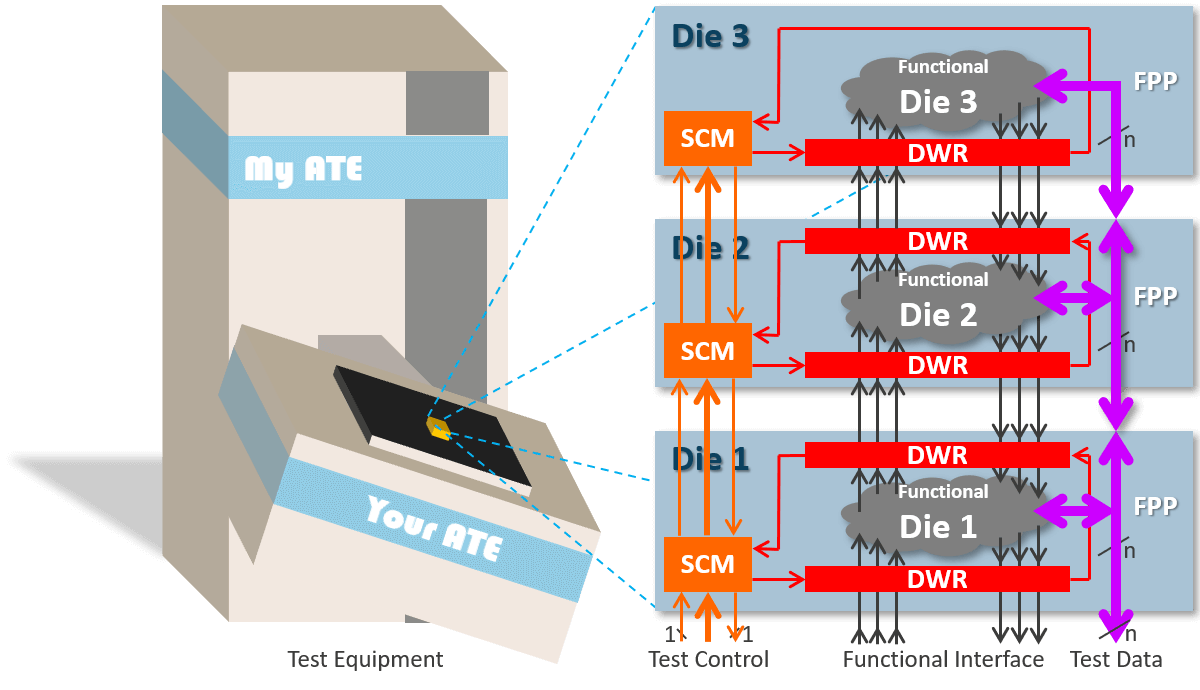

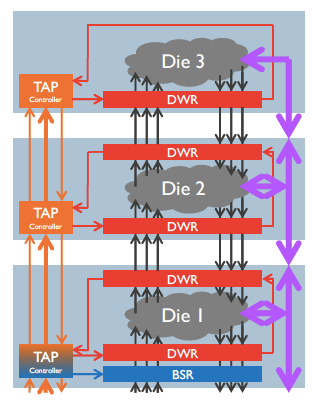

Marinissen explained that IEEE 1838 specifies what DfT features are mandatory to include in each die at a minimum, while also having several optional features. Figure 1 depicts the three main components of the new standard:

- A die wrapper register (DWR) to enable modular testing at the die and interconnect levels. A wrapper isolates the die-under-test from its environment.

- A serial control mechanism for low bandwidth test access to handle loading instructions and/or slow test data.

- An optional flexible parallel port (FPP), unique to IEEE 1838, that allows for high-bandwidth test access and is configurable according to user-defined specifications.

“The die wrapper tells you what happens between the dies in the stack and in the interconnects,” said Marinissen. “On-chip ‘test elevators’ allow you to transport test stimuli from external test equipment into stacked dies and test responses via a similar route in the opposite direction back out to the test equipment for evaluation. However, these test elevators need to be compatible with the various dies in the stack.”

“The standard specifies what 3D-DfT features should and/or could be implemented in dies. This allows for interoperability between die maker(s) and the die stacker,” he added. “The 3D test wrapper has standardized features, but at the same time provides quite some configuration options. That is why I believe the 1838 Working Group should continue to work on a standardized formal description language.”

“A description of optional features included in the delivered 3D-DfT wrapper should be described in a standardized language. Unfortunately, that part of the standard didn’t coalesce in time,” explained Cron. “The working group opinion diverged into many different directions. Ultimately, it requires adapting an existing description language that describes which features of IEEE 1838 have been implemented in the chip.”

The situation is similar to IEEE Std 1149.1, which was first released back in 1990 with only specifications for on-chip DfT hardware, while the corresponding boundary-scan description language (BSDL) was only added to the standard in 1993.

“The language might come after the initial release of the standard because it requires a different set of people to develop,” explained Marinissen. “There are hardware people and software people. The 3D Test Working Group might continue its standardization work by defining a language as its next task. In the meantime, we will release the standard for hardware and the language can be worked out by the users.”

Why is IEEE 1838 Important to 3D ICs?

“Essentially, IEEE 1838 provides a coherent stack-level test access architecture that can pump stimuli arriving from external test equipment into a die-level test infrastructure. It also defines infrastructure to support interconnect test between the die by adding additional or leveraging existing circuitry on the chip to facilitate test access,” explained Cron. He added that the DfT infrastructure is designed to be used throughout the lifetime of the chip. Test and debug back doors are part of the design, allowing for one-bit-in/one-bit-out access, even if the chip is packaged and installed. It can be programmed to access stack-level DfT via a serial test access mechanism. It can also be set up to leverage infrastructures to provide information about why things fail or no longer work.

While no standard is mandatory, it does help the industry progress more quickly to make plug-and-play technologies, noted Cron. “Synopsys has supported me for years in developing standards,” he said. “That way customers can focus on functional creativity rather than worrying about test. Adopting a standard makes test easier for them.”

For example, IEEE 1838 is expected to be fully compatible with chiplet stacking, the latest game-changer in heterogeneous integration. While there are a variety of chiplet approaches, the heavy interconnect between the dies that rely on directionality to interconnect is similar. They can be built with the 3D DfT standard in mind, says Cron.

If your employer subscribes to IEEE Explorer, you may have free access here. Otherwise, purchase your copy here.