In the past, the Design Automation Conference was known to me and many of my colleagues as the annual event that focused on IC design tools, flows, and methodologies. EDA tools vendors and users got together in the previous millennium to discuss what to do next in a rapidly growing market segment. Then things changed…

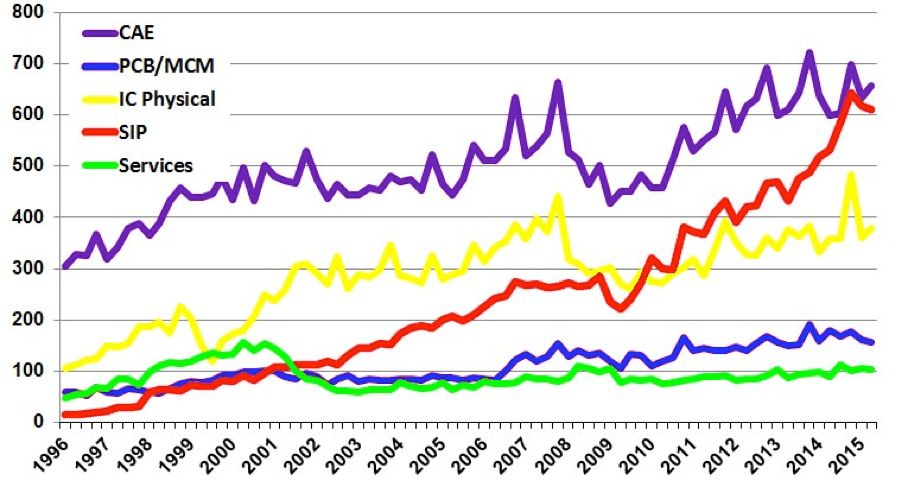

At the beginning of this millennium, the wafer foundries took charge of silicon manufacturing and many IDMs became fabless or at least fab-lite. In addition, many smaller ASIC vendors “retrenched” from selling packaged ICs to offering soft or hard semiconductor IP (SIP) (See SIP growth, in red below). As the EDA Consortium’s Market Statistics Service (MSS) has clearly demonstrated over the years, SIP became the fastest growing portion of the EDA industry.

Now that the EDA industry digested the business model change from IDMs to fabless & foundry partners and learned to respect and cooperate with the few, but very powerful wafer foundries, it’s high time to get ready for another major technology and business model change.

As almost 500 pages of detailed information in the 2016.6 edition of the Multi-die IC User Guide demonstrate, many EDA vendors, Design Services, IP providers, Assembly & Test houses (a.k.a. OSATs) and their suppliers, R & D partners, industry organizations and others are already fully engaged in the semiconductor industry’s transition from transistor scaling to system scaling. In addition, the EDA Consortium (EDAC) changed its name to Electronic System Design Alliance and has refocused its mission and activities to system scaling.

After this lengthy introduction and regression analysis of 50 years of transistor scaling, let’s use DAC 2016 as an additional data point to fine-tune our projections for our industry’s future.

Like in previous years and again in 2017, Austin’s Convention Center hosted DAC 2016. About 30 new companies showed their strengths, this means that 20% of the exhibitors were new; a remarkable and very positive sign that there is new life in the EDA and IP industry. As the title of this blog and the content of this year’s DAC keynotes suggest, there is more to life – and obviously also to the EDA industry – than the traditional IC design challenges.

Monday morning started out with a very impressive keynote from Lars Reger, CTO of NXP’s Automotive Business Unit. Like most Germans and me, he loves cars. His enthusiastic talk about the future of cars showed that NXP picked the right man to drive IC solutions for the rapidly growing automotive applications. Equally, if not more important, was NXP’s acquisition of Freescale, a well-established IC supplier to the automotive industry. Reger picked a very compelling way to tell us how important it is to complement human driving skills with electronic smarts:

- 94% of the worldwide 1.3 million traffic fatalities per year are caused by human error!

- In addition to this death toll, 50 million people get seriously injured every year on our roads.

Reger reminded us of the stringent quality and reliability requirements in the automotive segment (e.g. as outlined in ISO 26262) and clarified the difference between safety (= car doesn’t harm anybody around) and security (= car doesn’t get hacked or otherwise influenced by external forces). He projected that for level 4 (= fully autonomous driving) between six and twenty radar modules, operating at 77 to 81 GHz, will be required to make a car smart, environmentally aware and safe to use (“operate” is no longer the right word!) on the road.

His example for the value of vehicle-to-vehicle communication was also very impressive. He told us that “truck platooning” is already available and showed how a number of trucks (like train cars but electronically “connected”) follow each other, just a few feet apart, to minimize wind resistance. Most important, all the following trucks don’t need drivers, because the leading truck commands them electronically. Knowing the progress of electronics in automotive, I dare to project that even the first truck won’t need a driver anymore in future.

Reger confirmed what I heard from other sources: The automotive industry is targeting the 1 Gbits/sec deterministic Ethernet standard for in-car communication. What they call the “Blue Box” will contain the vehicle’s central computer and manage up to 250 domains on the car’s network. Like in airplanes, automotive electronics will need redundancy to meet the very high-reliability requirements and also initiate frequent self-checks, to operate safely and securely all the time and under any operating conditions.

Just to top off his impressive presentation, Reger pointed at the ring on his left hand and told us that it contains a clock-less (= extremely low-power asynchronous) NXP circuit for near-field communication. Instead of using – and possibly losing – today’s clunky keys, you simply wear a wedding ring. He didn’t recommend what unmarried people should do…

Tuesday’s keynote was delivered in two parts: Lou Scheffer, Principal Scientist at Howard Hughes Medical Institute in Maryland presented how biology outperforms modern electronics in regards to performance per Watt, resilience, self-assembly and repair, and even self-learning. Scheffer presented examples from humans and the animal kingdom, down to “primitive” self-learning bugs, and encouraged us to learn from nature how to make our sophisticated electronic equipment even more amazing. As I watched other people in the audience, I could tell that I was not the only one who faces a very steep learning curve to observe, analyze, and interpret nature’s ways of doing things and then transfer them into electronics.

Sameer Halepete, VP of VLSI Engineering at Nvidia, used a vocabulary and principles I could follow and understand. He focused his talk on three important requirements:

- The need for speed: To make gaming applications look realistic, very high performance is needed. Likewise, simulations benefit significantly from higher performance. According to Halepete, the rapidly emerging virtual-reality (VR) equipment and even more the augmented reality (AR) equipment needs seven times the performance of gambling to become user-friendly. He proudly mentioned, that 80% of today’s high-performance computers use GPUs.

- The need for self-learning equipment and artificial intelligence: Excellent Image recognition and fast computing algorithms, as well as hardware, are needed to make significant progress in this area. As an example for Nvidia’s high-performance solutions, Halepete mentioned their recently introduced P100 System. At its core are a GPU and four high bandwidth memory (HBM) cubes on an interposer.

- The need to manage design complexity: For their very large designs with up to 15 billion transistors, they, of course, use hierarchical design methods today but find that much better Verilog code linting is needed to minimize iterations and endless hours of simulations. Halepete also stated that manually generated RTL code is still better that high-level synthesis results. Sign-off quality RTL simulators, better ways to achieve timing and power closure and better tools for testability of very high complexity designs are also on his wish list for EDA vendors.

Wednesday’s keynote was presented by Mark Papermaster, CTO and Senior VP at AMD.

Unlike the mostly technology-focused messages we typically hear, Papermaster shared his management experience gained at IBM, Cisco, Apple and now AMD. Titled “The Challenge to Develop Truly Great Products” his message briefly covered our industry’s PC era, then the internet and smartphone dominated years. With the end of Moore’s Law in sight, Papermaster stated that we are now in the immersive era. (Immersive pertains to digital technology or images that deeply involve one’s senses and may create an altered mental state.)

To build a great product, he suggested to ask yourself first a few basic questions: What problem will it serve? What impact will it have on innovation? Will it offer a better user experience than existing alternative? Looking back at great products, Papermaster listed iPod, iPhone and gaming consoles. Looking forward he expects virtual reality and augmented reality products to be added to the list of great products.

After targeting the right product, Papermaster suggested we set clear goals and develop a plan for building the great product. Before starting to build the product, management needs to build the right team and instill the right culture into the people to guarantee maniacal execution (Mania is defined as excessive excitement or enthusiasm). For the development plan, he suggested clarity, contained scope, simplicity and high-level as criteria for success. In addition, Papermaster recommended involving outsiders and fresh eyes to refine and enhance the planned product.

Then he defined detailed key criteria for the right culture. Good listeners and team members who can inspire people are important. Transparency makes conflict resolution easier. When making decisions a willingness to take risk is essential. All these elements will contribute to building trust among the team members and with management.

As next step, Papermaster described key criteria for building the right team. He suggested a mix of broad system thinkers as well as deep and narrow domain experts. Someone should play the role of devil’s advocate. Adding dreamers and pragmatists round out the right team.

Maniacal execution was his final success criteria. Establishing clear metrics, risk milestone management and owning your dependencies are Papermaster’s recommendations.

By mentioning that VR will be a $80B market (according to Bloomberg) he gave us a peek into AMD’s product plans. Papermaster clearly sees VR and especially AR to dominate the immersive era and provide value for entertainment, gaming, training and simulation. In addition, education, as well as big data analysis, will be important emerging applications.

Enough said for part 1 of the DAC report. Allow me to add now a hopefully very useful topic for you: On Wednesday, June 22, I’ll be moderating a webinar at Open-Silicon. Experts from Hynix, Synopsys and of course Open-Silicon will outline in just one hour a lot of useful info about how to break down the dreaded memory wall to increase bandwidth and reduce latency, power dissipation and form factors of your systems. Register here.

Also, don’t forget to download – at no charge – from the ESD Alliance’s home page the 2016.6 Multi-die IC Design Guide.

As sensors and actuators are becoming more important to make our electronic systems environmentally away, the Sensors Expo & Conference in the San Jose convention Center on June 21 – 23 will update you. Details and registration info is at www.sensorsexpo.com. ~ Herb