Product Description

Product Description

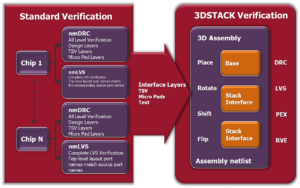

Calibre enables signoff verification of chip stacks with flip chips, silicon interposers and through-silicon vias (TSVs). Verification of individual dies is followed by checks on the interfaces between dies, including dimensional checks (bump alignment and rotation), connectivity checks (LVS), and parasitic extraction (PEX) using a special 3D-IC rule file.

Testimonial

Calibre allows designers to maintain standard DRC, LVS, and PEX verification flows while enabling multi-die 3D interface verification. Using package information (die order, x/y position, rotation) in a rule deck, Calibre performs all DRC and LVS checking of complete multi-die 2.5D-IC and 3D-IC systems. It verifies physical attributes (offset, scaling, etc.), and traces the connectivity of interposer or direct die to die connections. Calibre also provides parasitics as individual chip netlists and a 3D stack top level netlist for simulation. It delivers these capabilities without breaking current tool flows or requiring new data formats. Calibre minimizes disruption to existing verification flows and provides designers with support for different process nodes and stacking configurations (interposer-based and full 3D). It also provides extendibility with the capacity to incorporate new extraction and verification solutions in the future.

- Mentor Graphics Website

- Date this Product was Introduced to the market: Oct. 2012

- Category Product is Being Nominated for: Design Tools

- Technical Information on Calibre

- White Paper on Calibre