I don’t know about you, but I always find that amidst the holiday hubbub, the really important stuff gets shoved aside and falls through the cracks. Just in case you missed them, here are some good 3D related posts that may have been lost in the December race to “get it all done” so we could enjoy the holidays.

On the topic of the 3D IC supply chain, SemiMD’s Mark LePedus wrote a comprehensive overview about the changing foundry landscape in the 3D space. In it, he reveals a shift in position by TSMC, quoting the company’s Chairman and CEO, Morris Chang. According to this post, TSMC is “rethinking its position” about insisting on providing end-to-end service for 3DICs, and is now willing to work with partner OSATS. This approach is more inline with the business model adopted by GlobalFoundries and UMC. LePedus also reports on the Tezzaron/Novati business model and the OSAT perspective.

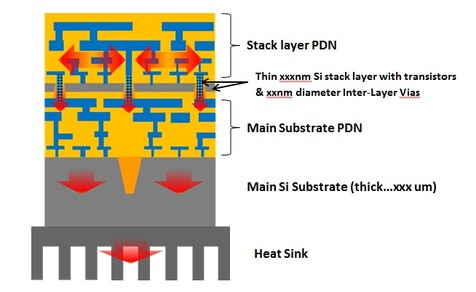

One of the remaining concerns with 3D ICs is how to get the heat out. Brian Cronquist, MonolithIC 3D Inc.’s VP of Technology & IP blogged about this just before Christmas, referencing a paper presented by Hai Wei of Stanford University, at IEDM last month that addressed this issue for both 3D ICs using TSV stacking (he calls this “parallel 3D ICs), as well as in fine-grain, monolithic (or sequential) 3D ICs. Rather than relying on TSV arrays and thick silicon layers to conduct and spread heat laterally, Cronquist proposes using “properly designed power delivery networks (PDNS)” that move heat laterally into the metal stack of each layer, and then vertically through the stack to the heatsink. He says this solution works for both “parallel” and monolithic 3D IC stacking.

These days we can hardly attend a 3D IC conference without a presentation by Xilinx on their success with their family of 3D IC FPGA products — aka 2.5D FPGAs. (Incidentally, at the 3D ASIP conference, Xilinx’ corporate VP, Liam Madden cleared up this issue quite nicely. “From an engineering perspective, its 2.5D. From a marketing perspective, its 3D. I think we shouldn’t get caught up in terminology.”)

With the addition of 3D IC FPGAs to the selection of programmable ICs, the question becomes, when to use which device. All Programmable Planet’s Max Maxfield posted a handy guide for determining when to use an all-programmable SoC vs. an FPGA or 3D IC . Beyond the detailed information in the post, what I found especially compelling is the beginning of the comment thread (56 in all, begin here) in which one reader questions why 3D ICs would even be interesting to an FPGA engineer. “So why does Xilinx keep harping on it? Does anyone (other than the packaging guys) really get all excited about the prospect of a “3D IC?” he says. Maxfield does a nice job of fielding that question “Well, I hate to say this, but I do (sheepish grin). I love technology in general. I remember when all we had was simple 7400-series devices and we thought they were incredibly cool. I’ve watched the industry evolve over the decades, and I think the current 3D ICs are just a taste of what’s to come”, and others. The discussion is quite interesting before it runs off topic to comparing organizational skills, among other things. (Happy Belated Anniversary Max! Hope Gina likes the gift!) ~ F.v.T.