In IFTLE 517, we discussed the upcoming standardization in the chiplet world with the passage of the Universal Chiplet Interconnect Express (UCIe) by member companies shown in Figure 1. With this powerhouse group agreed to all be on the same page, will anyone else go off on their own? IFTLE doubts it.

- The UCIe 1.0 specification provides a complete standardized die-to-die interconnect with physical layer, protocol stack, software model, and compliance testing to enable end-users to easily mix and match chiplet components from a multi-vendor ecosystem for system-on-chip (SoC) construction, including customized SoC.

- The UCIe 1.0 specification leverages the well-established PCI Express® (PCIe®) and Compute Express Link™ (CXL™) industry standards.

- UCIe supports different data rates, widths, bump pitches, and channel reach to ensure the widest interoperability feasible.

- Packaging bump density (advanced and standard) and per wire rate will determine bandwidth density.

- Each UCIe participant determines their own product roadmap and availability

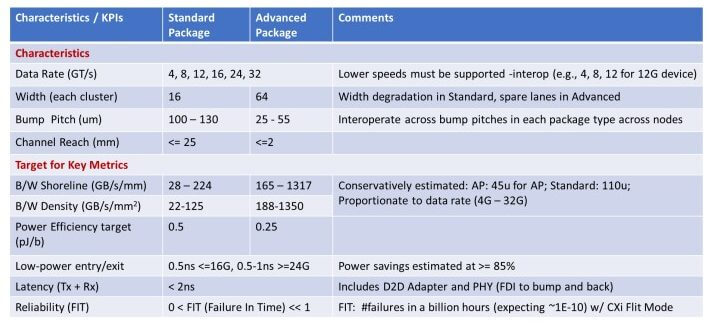

UCIe 1.0 defines two types of packaging. The standard package (2D) is used for cost-effective performance. Advanced packaging is used for power-efficient performance. Table 1, taken from the UCIe white paper, Universal Chiplet Interconnect Express (UCIe)®: Building an Open Chiplet Ecosystem by Debendra Das Sharma of Intel discusses the key metrics for both the packaging options.

A die with the standard package design is expected to operate with any other design on the standard package. Similarly, a die with the advanced package design will interoperate with any other die designed for the advanced package, even within the wide range of bump pitch from 25µm to 55µm.

It should be noted that the table conservatively estimates performance for the most widely deployed bump pitch today. For example, 45µm bump pitch is used for advanced packaging. The bandwidth density will go up by up to 3.24X if we go with a denser bump pitch of 25µm. Even at 45µm, the bandwidth density of 1300+ is about 20X which can be achieved with the most efficient PCIe SERDES. Similarly, PCIe PHY has a power efficiency of ~10pJ/b today, which can be lowered by up to 20X with the UCIe-based designs due to their shorter channel reach. UCIe also enables very fast entry and exit times (sub-ns vs multiple micro-seconds for SERDES-based designs) while saving 90+% power. Thus, in addition to reportedly being really low power, it also appears to be very effective in power savings. In addition, they predict that as the technology advances, these savings will be even more significant. They report that UCIe 1.0 has been defined to meet the projected needs of a wide range of applications through the end of this decade.

The full specification can be requested on the website.

Importantly, Intel has indicated that UCIe specification will include details on interoperation with AIB-based chiplets. When asked about compatibility with their AIB protocol that they have been pushing for the past 2+ years here were their responses.

Q: Will Intel continue to develop products using the current AIB specification?

A: Yes, new products will use today’s AIB interface, along with several being developed in concert with the US Government State-of-the-Art Heterogeneous Integration Prototype (SHIP) program.

Q: Will UCIe support AIB?

A: Yes, the UCIe specification will include details on how UCIe implementations can interoperate with AIB-based chiplets, enabling AIB-based chiplets to join and contribute value to the UCIe chiplet ecosystem.

Q: What are Intel’s plans for AIB going forward?

A: Intel is committed to UCIe and we will migrate AIB applications to UCIe eventually. The latest AIB 2.0 specification is being used now by developers for new chiplets. We do not expect any new spec development beyond AIB 2.0 given the UCIe path. We expect that many AIB developers will benefit from and seek to transition to UCIe to take full advantage of the improved KPIs. Developers using UCIe will be able to take advantage of UCIe/AIB super-set PHY to access the AIB chiplet ecosystem.

All in all, great news for those wanting to see chiplets become an integral part of the available packaging technology options.

For all the latest in Advanced Packaging stay linked to IFTLE………………….