I attended the 3D IC Technology Forum at SEMICON Taiwan 2014, where many of the discussions focused on the latest memory announcements in 3D ICs from Micron, SK Hynix, Samsung, and Tezzaron. While the world still waits for the introduction of a Wide I/O mobile DRAM and logic part, memory is clearly moving into production.

The focus of Taiwanese OSATs in the 2.5D space, such as SPIL and ASE, is to work with interposer suppliers to provide processing after the vias are fabricated and provide assembly of the die on the interposers. SPIL described its focus on enabling 2.5D assembly and working with multiple foundry partners. Research in overcoming challenges such as substrate warpage was discussed. ASE described its readiness for middle-end-of-line (MEOL) and 28nm silicon node top-die assembly. Reliability data for the 8mm x 8mm ASIC mount on an interposer was presented.

The ability to partition a design so that only the critical features are fabricated in the newest (most expensive) technology node has clear cost advantages. This includes considerations for mask cost, defect density, and yield. Inotera Memories described its interposer offering and exclusive partnership design with ASE. The relationship started two years ago and is being promoted as a fast cycle time potential for silicon interposer design and assembly. Inotera repots that interposers up to 24mm x 36mm can be fabricated with 40µm micro-bump pitch and RDL on both sides of the interposer.

Mentor Graphics provided insight into integrated design with 2.5D and 3D ICs. Optimal Plus highlighted leveraging of smart screening and smart pairing to reduce cost in 2.5D and 3D IC, emphasizing the importance having a good die stack. IBM and Senju discussed the injection molded solder technology for solder bumping on wafer and laminates—pointing out the need for fine pitch bumps in the future.

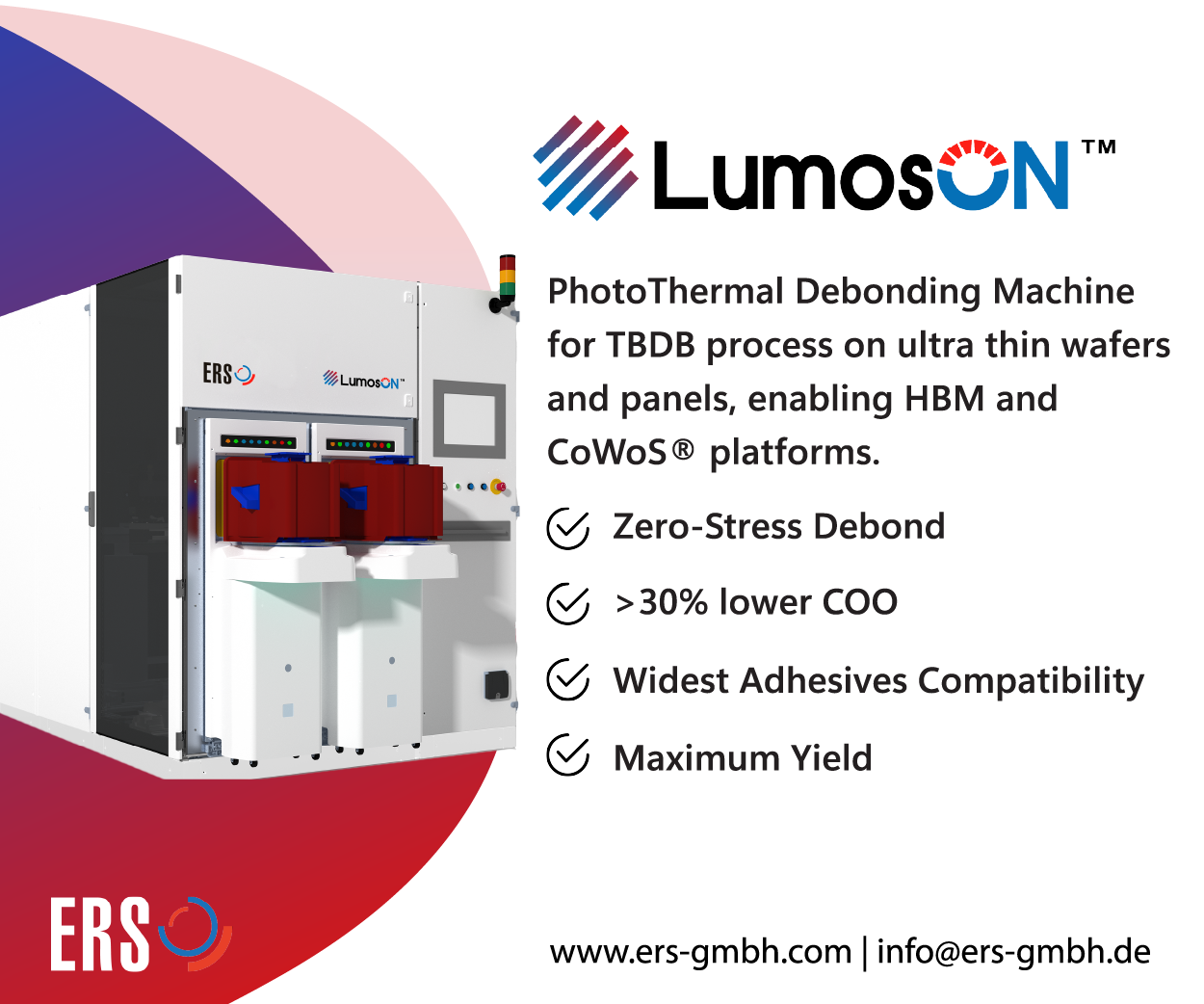

Presentations from equipment vendors SUSS MicroTec and EV Group highlighted the advances in equipment and the plethora of materials that have emerged for the bond/debond process—a step in the 3D IC process that requires yield improvement to lower cost.

IMEC’s presentation focused on advancements researchers have made to solve issues that slow adoption of 3D ICs. IMEC’s process of record (POR) is 5µm vias with a depth of 50µm and research is focused on even smaller vias of 3µm or even 2µm diameters. Challenges in scaling micro pitch down to 20µm were highlighted. IMEC described the importance of a good CMP that produces a flat surface in the hybrid bond process.

The panel discussion included the importance of wafer edge processing, the potential for permanent bond as an alternative to temporary bonding, and thermal management needs. Thermal design tools were highlighted as critical to the success of future implementations. ~ Jan Vardaman