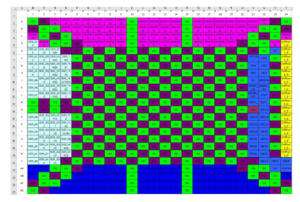

Traditionally, MCMs (Multi-Chip-Modules) were a way of integrating several ASICs, or ASICs and memory, into a lower-cost, smaller form-factor, robust module that was an alternative to a single large SoC. Instead of integrating all or most of the systems PCBs needs onto a large and complex single SOC, you could design and fabricate smaller, high-yielding ASICs (Figure 1) and make them behave like a single large SOC. This proved attractive in the defense and aerospace markets where volumes are lower than in the consumer commercial market and where trying to create a mixed technology SoC would be either impossible or cost prohibitive.

Traditionally, MCMs (Multi-Chip-Modules) were a way of integrating several ASICs, or ASICs and memory, into a lower-cost, smaller form-factor, robust module that was an alternative to a single large SoC. Instead of integrating all or most of the systems PCBs needs onto a large and complex single SOC, you could design and fabricate smaller, high-yielding ASICs (Figure 1) and make them behave like a single large SOC. This proved attractive in the defense and aerospace markets where volumes are lower than in the consumer commercial market and where trying to create a mixed technology SoC would be either impossible or cost prohibitive.

As the market for mobile wireless-enabled products exploded, along came a new demand for signal processing, flash memory, and wireless communications in a system that could fit inside a product smaller than a human hand and be cost effective. This challenge drove a different approach to packaging, and led the industry to 3D chip stacking of bare die.

This approach, referred to as systems-in-package (SiP), required interconnections from die-to-die so that the package became a critical technology element of the system PCB. Some view SiP as a vertical MCM, in contrast to horizontal MCMs, made popular in high-performance computing applications. Benefits to SiP include user IP integration, IP reuse, mixed analog/digital design, low design risk, integration of large memories, reduced process complexity, low developmental cost, and shorter time to market.

Perfect for heterogeneous applications, this building-block approach can be attractive to anyone looking at integrating ASICs into a high-performance sub-system with performance that is close to that of a custom SoC for a fraction of the cost and time to market. In short, SiP brings together ICs, including SoCs and discrete components, using lateral or vertical integration technologies. In this paper we will focus on the design of a SiP that is part of a known PCB system, which is a common occurrence in systems companies. In such a scenario, the SiP not only needs to meet the integration and performance goals as an integrated set of heterogeneous ICs but also must be optimized for its target system’s PCB, or even PCBs.