As you all may know, in most fan-out wafer level packages (FOWLP) such as embedded wafer level ball grid array (eWLB) by Infineon and STATS ChipPAC, and TSMC’s integrated fan out (InFO), the chip(s) are embedded in epoxy molding compound (EMC). Additionally, in some fan-out panel-level packaging (FOPLP) such as those being built by Fraunhofer IZM and J-Devices, the chip(s) are embedded in EMC. Other companies, such as AT&S, Unimicron, and Imbera, are embedding chips in a laminate organic substrate.

In my opinion, in general, chips that are embedded in a laminated organic substrate cannot be larger than 5mm x 5mm, due to the thermal expansion mismatch between the silicon chip (2.5×10-6/oC) and the organic substrate (15×10-6/oC – 18×10-6/oC).

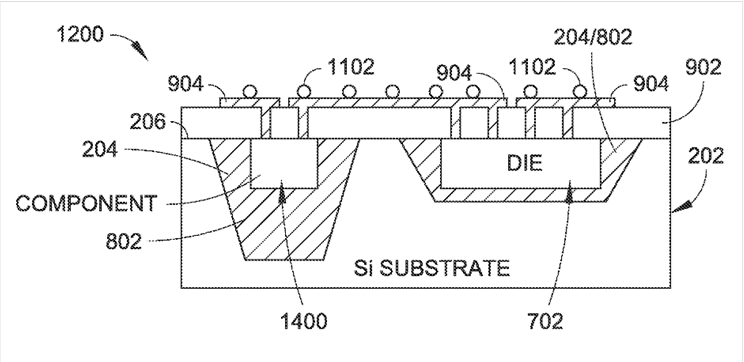

On June 28, 2013 (priority date: March 5, 2013), Maxim Integrated filed a patent (US 20140252655 A1), for an invention by Khanh Tran, Arkadii V. Samoilov, Pirooz Parvarandeh, and Amit S. Kelkar, “Fan-out and Heterogeneous Packaging of Electronic Components,” proposing to embed the chip(s) in a silicon substrate (Figure 1). A paper was presented during the IMAPS International Conference.

Again, my opinion is that, in general, the size of the chip cannot be larger than 4mm x 4mm (or the size of the silicon package cannot be larger than 5mm x 5mm). This is because of the thermal expansion mismatch between the silicon (package) substrate (not the chip) and the PCB (18×10-6/oC).

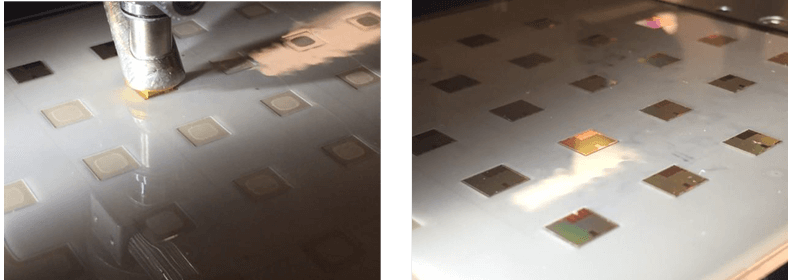

On May 31, 2017, at IEEE ECTC, George Institute of Technology (GIT) will present an alternative to EMC, organic laminate, and silicon, by presenting the very first demonstration of chips embedded in a glass substrate for FOPLP (Figure 2). The paper represents a collaborative effort by GIT, Schott, Asahi Glass Co., Ltd., and DISCO Corporation.

Will this glass fan-out (GFO) technology popular? I cannot tell. But, at least, it adds a new direction in fan-out packaging! ~ J. Lau

Nice article!

After fumbling around for years trying to push glass as a lower cost replacement for Si in 2.5d interposers, the GIT group seems to have finally accepted its limits ( slower rate in etching TGVs, hence higher cost ) and instead have started leveraging its inherent strengths ( lower tan delta : great for front end in LTE 5, RF does n’t require too many vias ) and the ability to tailor CTE to match various packaging materials ( from Si to organic ) as in the embedded package to be presented at ECTC 2017 ( something like that was done at GE way back in 1990 by Bob Wojnarowski ), but even w/o any embedding glass is a great temporary back up material during processing ( not just 300 mm but at up to panel sizes ), since it reduces warpage during processing, thus enables finer L/S. Coreless substrates processed that way are being used in flip chip packages that give interconnect density, DTR just as good as the much ballyhooed FO WLP but at a lower capital cost. Qualcomm uses it for their latest AP.

Hi Dev,

Perhaps you are a bit behind the curve these days on glass, there are many highly respected substrate companies who see the benefits of a glass core for advanced substrates in panel form for SiP applications.

Even the so called “Ultra” HDI applications are looking to utilise glass to allow them to use the inherent properties of the glass, flatness in particular to create finer lines and space for HDI applications, so there is a good chance in my opinion that it becomes mainstream for advanced substrates next year.

Glass drilling is now at circa 10,000 holes per second so has decreased dramatically in cost. As usual the industry will decide, based on cost and performance, in that order.

Robin Taylor

the idea of using a glass core matched to the CTE of Si is not new, it is especially useful for MCMs that use large Organic substrates ( issues of CTE related warpage during assembly etc. ), at both Motorola and Intel had tried some of Rao’s “old love” of CTE matched glass ceramics as cores for Organic BU layers, but routability was limited due to through via issues, had suggested that Rao look into glass cores as an opportunity for his glass panels, but that was 7 years ago, have n’t seen any activity / papers / products yet. Twenty years ago had taught and managed the pioneers of Organic substrates ( all still in Japan ) HVM of FC substrates at high yield and made it possible for FC to transition from ceramic to now standard organic substrates. You sell plating chemicals in the UK, that too for Germans who since WW II ( Radar ) have always been followers in electronics, so who are these ” many highly respected substrate companies who see the benefits of a glass core for advanced substrates ” that you mention ? And your closing remark “the industry will decide, based on cost and performance, in that order” takes the cake as a statement of, as BASIL FAWLTY might have said, the BLEEDING OBVIOUS !