It all depends upon who you talk to at IEDM 2023. The semiconductor chip industry is either moving into a new realm that will be based upon chiplet technology, or the industry is continuing to drive front-end and backend technology forward and the two technologies are morphing together to drive Moore’s Law advanced compute forward as it has for the past 60 years.

IEDM 2023 was the 69th meeting of the IEEE Electron Devices meeting, and everything was back in full swing. After a couple of years of online and online, in-person hybrid the conference is now back to predominately in-person, but they do have an option to review videotaped presentations, which enables those with multiple areas of interest to go back and view the conference and refresh their memories when writing about the conference.

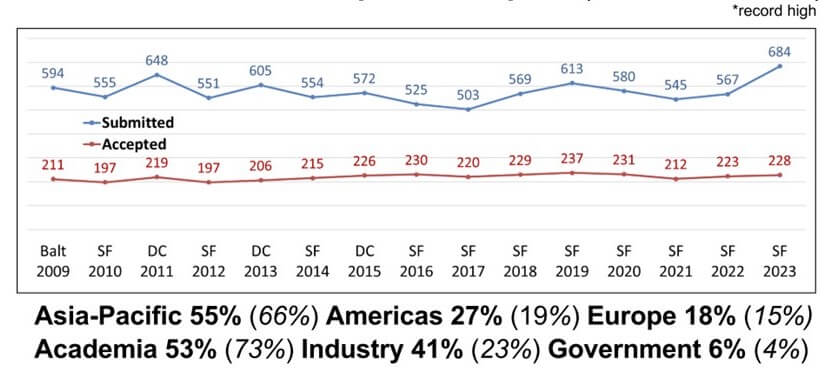

IEDM 2023 By the Numbers

The conference’s focus was Devices for a Smart World Built Upon 60 Years of CMOS. There were 684 papers submitted and 228 selected by the committees. The split of accepted papers was 53% were academic, 41% from Industry, and 6% from government institutions. On the academic side, a significant amount of the research is funded by government grants, DARPA, SRC, and others.

With all of the discussions about the Chips Act, it was interesting to see that 55% of the accepted papers were from Asia Pacific, (AP), 27% from the United States, and 18% from Europe. The larger number of papers from AP has been the trend for several years, but to a certain extent, it reflects the fact that AP has a significantly larger focus on advanced semiconductor R&D than is taking place in the United States. It will be interesting to see if the increase in focus on semiconductor education funded by the Chips Act moves the needle on papers published in the United States and Europe.

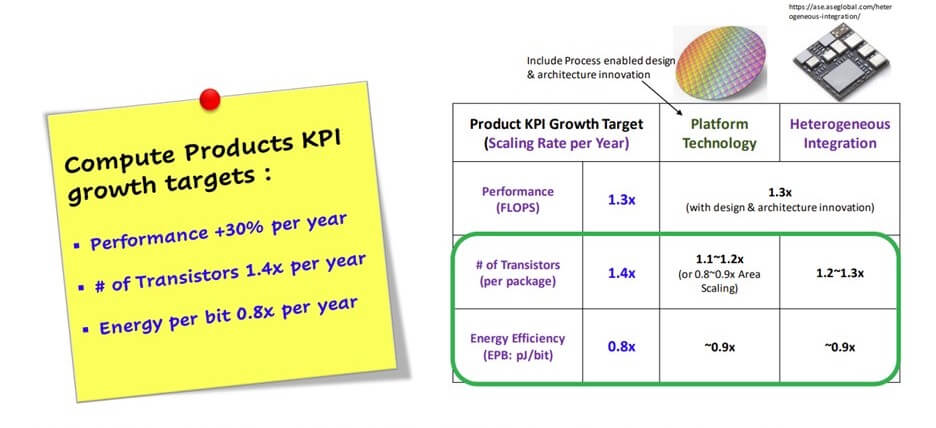

At IEDM, my primary focus is on understanding where the leading edge is going, and how it is proposed the industry will get there. I always enjoy when the technologists start to get involved in the marketing hype about where the industry is headed. While on one side the industry has been talking about $1 trillion in revenue for the semiconductor industry, there is now considerable hype over the industry reaching one trillion transistor integrated circuits (ICs). Currently, the Apple M1 SoC has about 117 billion transistors, and the Intel Ponte Vecchio, which is a chiplet, has 100 billion transistors. To achieve the 1 trillion transistor number will require an increase of 10x over the next several years. The question is how does the industry get there?

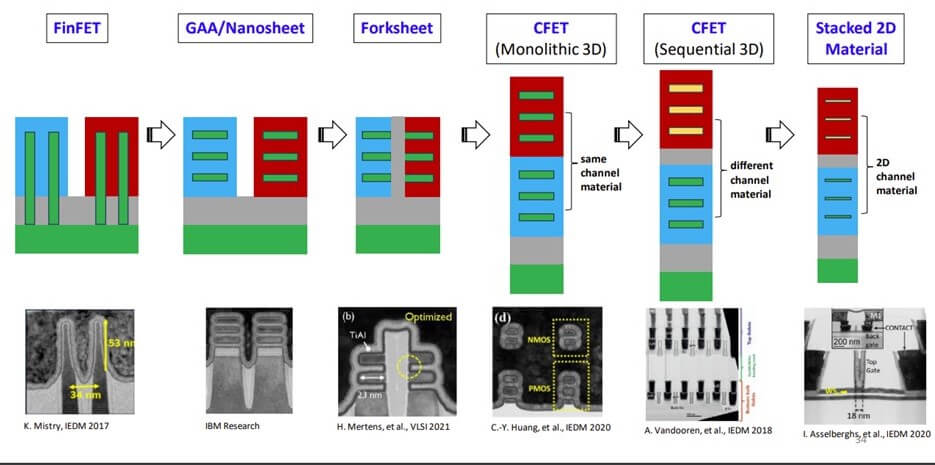

From the papers at IEDM, the approach will be two-fold. One will be continuing to improve chiplet technology to increase the number of processors and memory that are placed together on the same interposer. The other is to move from the current finFET technology to Gate All Around, (GAA) to monolithic CFET technology to eventually 2-dimensional channel materials using the CFET template. Jie Deng of Qualcomm pointed out that in addition to integrating the CFET and the packaging technology, the platform technology will need to look at how to integrate everything best together to create the next-generation system in a package (SiP).

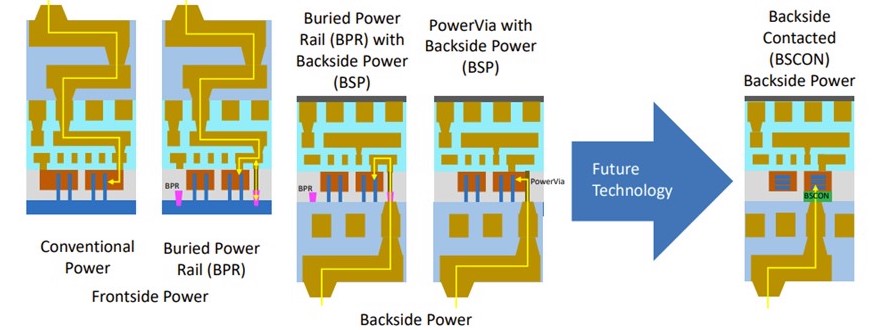

While transistor technology is evolving to achieve one trillion transistors, interconnect technology needs to evolve as well. Intel is implementing backside power delivery to help improve interconnect performance and help reduce process complexity. It is also hoped that implementing backside power will help to reduce the heat generated by the chips and chiplets, which is one of the key issues that must be considered in the system design. Especially from a sustainability perspective in data centers.

One of the keys to success in chiplets is solving the memory wall. This problem is two-fold:

- In-chip memory SRAM cache. Can it continue to shrink at the same rate as the logic transistor, and can it meet the needed speed requirements for the processors of the future? Embedded MRAM is emerging as an alternative to SRAM the advantage is that MRAM can be embedded into the interconnect and potentially reduce the area requirements of the SoC or Chiplet. However, overheard in conversations at the conference was the old, the best replacement for SRAM is SRAM. This also goes for DRAM and NAND flash, as better alternatives are still being looked for.

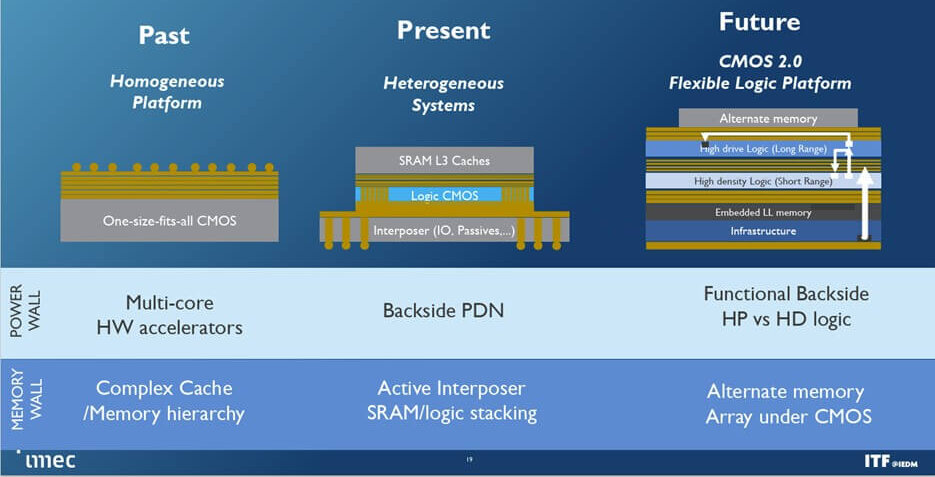

- High bandwidth memory (HBM) DRAM implementation, which was a hot topic at IEDM. This technology is moving forward quickly but still has data transfer challenges that generate heat. Figure 5 shows IMEC’s version of the Heterogeneous Integration Roadmap for the onboard, or in-chiplet memory challenge.

When you consider that historically every 2 years the industry has doubled the number of transistors per unit area, and the industry currently is at 100 billion transistors on an SoC, and that Moore’s law has also been expanded a bit to consider the number of transistors per unit area. If the industry keeps on track the number of transistors in a chiplet package should exceed a trillion sometime in the 2028–2030 time frame. From the conversations at the IEDM, the keys to achieving this success appear to be in stacking the transistor, improvements in interconnect density and RC, and finding a solution to the memory wall to reduce the amount of power both consumed and produced by the systems of the future. At this moment I’m betting on reaching one trillion transistors before one trillion dollars.