This year’s Design Automation Conference (DAC 2018) was held at Moscone West, San Francisco, CA. On three levels, about 175 exhibitors showed their capabilities and discussed market needs. Our industry’s focus on artificial intelligence (AI) and machine learning (ML) solutions were clearly obvious, and I suspect, attracted more young people and a fairly large number of new exhibitors to DAC than in previous years. Great news!

This year’s Design Automation Conference (DAC 2018) was held at Moscone West, San Francisco, CA. On three levels, about 175 exhibitors showed their capabilities and discussed market needs. Our industry’s focus on artificial intelligence (AI) and machine learning (ML) solutions were clearly obvious, and I suspect, attracted more young people and a fairly large number of new exhibitors to DAC than in previous years. Great news!

More good news for electronic design automation (EDA) companies and their shareholders came from Jay Vleeschhouwer, an EDA financial analyst at Griffin Securities. He confirmed that EDA vendors are growing, both revenues and profits, especially in IP. As systems companies develop more chips themselves, this market segment is also becoming an important revenue source for EDA. As evidenced by the many job openings, EDA vendors clearly demonstrate that they are optimistic about the future.

Dr. Walden Rhines, CEO of Mentor, a Siemens Business, confirmed this trend during Monday night’s dinner. When he talked about the success of Mentor’s integration under the Siemens umbrella, he stated that Mentor’s departments grew from 15 to 35% over the last year and significantly above industry trends.

In my 25+ years in the ASIC business, I have learned the hard way how important EDA tools are for first-time success, cost reduction, time to market, for improving an IC’s performance per Watt, reliability, etc. As more of the IC value creation is moving to IC packaging, I am pushing for closer cooperation between EDA and packaging experts. That’s why I was very happy to hear from Bob Smith, Executive Director ESD Alliance, representing EDA and IP companies, that they agreed to become a strategic association partner with SEMI, the industry organization dedicated to serving the entire semiconductor supply chain. This expands the ESD Alliance’s reach worldwide and across the entire supply chain and contributes to improving manufacturing efficiencies and expands SEMI’s reach into EDA/Design. Smith’s blog “No Design is an Island”, tells you more about the strategic importance of this partnership.

Monday morning’s ARM – TSMC – Synopsys breakfast presentations also showed how important cooperation across the supply chain is. ARM highlighted their POP IP User Guide. TSMC confirmed that risk production for N7 is ongoing and N5 will start 2Q’19. Synopsys outlined their Fusion Platform and emphasized the importance of pre-beta cooperation.

DAC keynotes demonstrated that big challenges AND opportunities are ahead for our industry. They were recorded!

Monday’s keynote speaker was Sarah Cooper, GM of IoT Solutions at Amazon’s Web Services. She emphasized that consumers’ ability and willingness to accept new technologies and services is increasing. Also, users like personalized devices, they even appreciate that their devices can learn what users want.

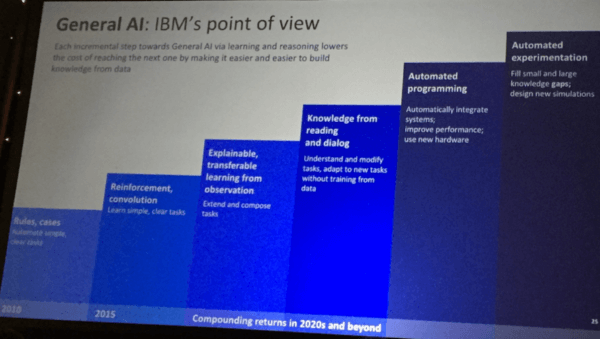

Tuesday’s keynote focused on AI and IBMs ongoing software and hardware developments in this space. Dario Gil, VP at IBM Research, talked about the future of computing and the impact ML, deep learning (DL) and AI have. He showed how rapidly the number of AI students at MIT and Stanford is increasing and explained why approximate computing is needed to increase performance per Watt. See in Fig 1 below IBM’s plans for the near future.

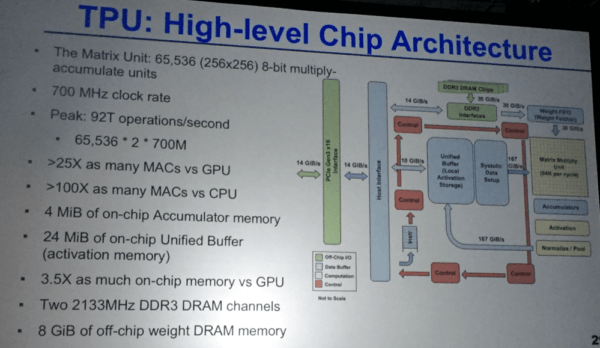

Wednesday’s keynote speaker was David A. Patterson, a key contributor at Google and Professor Emeritus at UC Berkeley. He talked about the history of computing, from the first reduced instruction set computer (RISC) chips developed at Berkeley and Stanford in 1982 to today’s RISC V technology. He outlined Google’s cloud tensor processing units (TPU) efforts and the RISC V architecture’s benefits (Figure 2).

If you want to know more about RISC history, fundamentals, security and computing architectures, please study the 6th edition of “Computer Architecture”, a book David Patterson and John Hennessy wrote and update regularly.

In addition to these keynotes, I had the opportunity to capture other interesting news at DAC 2018.

Here are some IC packaging focused presentations:

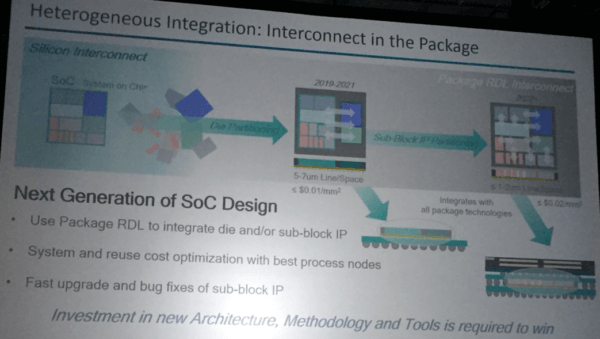

Qualcomm’s VP Engineering, PR “Chidi” Chidambaram, delivered a visionary talk about 5G and the increasing importance of IC packaging. (Figure 3).

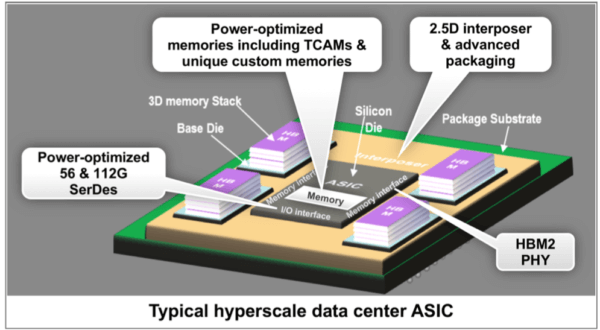

eSilicon announced the availability of a highly configurable platform, that combines the benefits of following Moore’s Law to 7 nm and applying More than Moore interposer technology (Figure 4):

Netspeed System’s CEO, Sundari Mitra, outlined benefits of their interconnect fabric. Then she discussed with Hideki Sugimoto, Board member and CTO of NSITEXE, a Denso subsidiary, its applicability for automotive. When I asked if this fabric can be applied to interposer designs as well, Mitra answered with a clear “YES” and emphasized that her team is ready to engage with customers in this space.

Imperas, a key member of the RISC V Alliance, explained the user benefits of their open source business model and the rapidly increasing number of Alliance members.

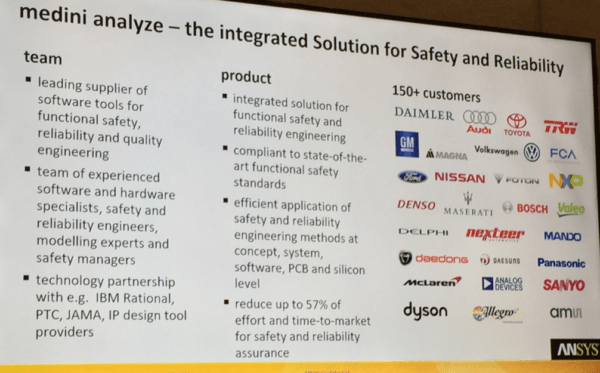

ANSYS is also growing rapidly and is now clearly # 4 EDA vendor, after Synopsys, Cadence and Mentor, a Siemens Business. I attended their “medini” presentation. It explained how this integrated design solution assures safety and reliability, in strict compliance with ISO 26262 (Figure 5).

Next year’s DAC will be held from June 2 to 6, 2019 in Las Vegas.

In addition, SEMICON West in San Francisco will include an EDA & IC Design section and demonstrate a big step towards bringing design and manufacturing closer together.

The many and rapid changes in our industry suggest that you keep up to date by attending industry conferences.

Please join me at:

SEMICON West in San Francisco, from July 9 to 12, 2018.

Electronic Design Process Symposium (EDPS) in Milpitas, CA, September 13 and 14, 2018.

International Wafer-level Packaging Conference (IWLPC), in San Jose, October 23 to 25, 2018.

Coming soon: Info about MEPTEC’s Annual Conference in Milpitas on December 5, 2018.

Thanks for taking time to read about my DAC observations! ~ Herb Reiter, Consultant for eda 2 asic manufacturing