At the Open Compute Project (OCP) / APAC Summit in Taiwan, S.Y Hou (Director of Advanced Packaging Integration, gave a presentation on TSMC Advanced Co-packaged Optics (CPO) Integrated using Chip-on-Wafer-on-Substrate (CoWos) and Compact Universal Photonic Engine (COUPE)

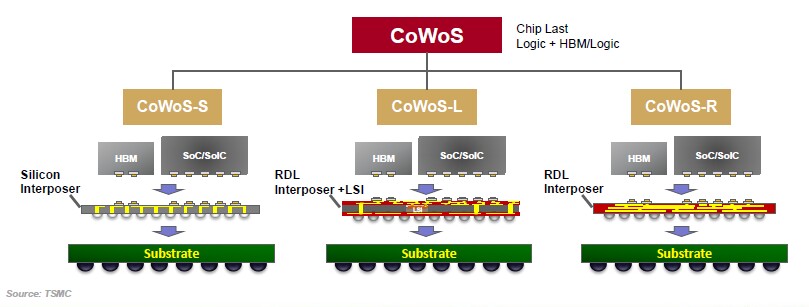

Readers of IFTLE are well aware of the TSMC CoWoS platform shown in Figure 1.

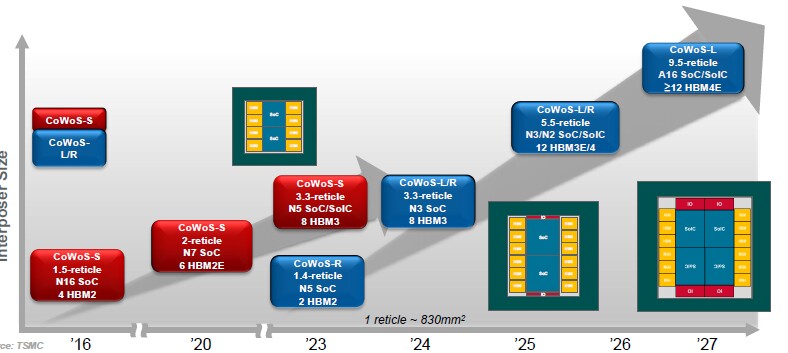

The CoWoS roadmap for enabling AI compute scaling is shown in Figure 2.

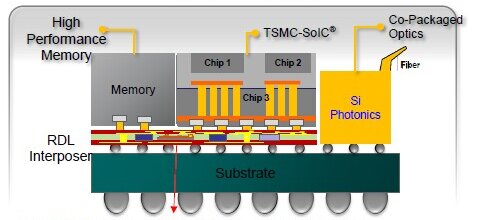

TSMC COUPE, however may be new to you. COUPE is based on TSMC’s System on Integrated Circuit (SoIC) stacking technology to integrate advanced logic on photonics IC (PIC) to form an optical engine.

SoIC is TSMC’s name for its 3D/chiplet integration family that enables chip‑on‑wafer, wafer‑on‑wafer, and other heterogeneous stacking approaches, with scalable sub‑10 µm bond pitch for very high density interconnects.

So, “SoIC” refers to TSMC’s overall 3D integration solution whereas “hybrid bonding” refers specifically to the bonding technology used within that solution.

TSMC reports that COUPE delivers a smaller footprint, high power efficiency, and excellent electrical and optical performance.

- Optical Engine (OE) based on COUPE enables high-bandwidth interconnect

- Packaging migration from Cu Wire to CPO offers more than 10X power benefit

- COUPE has been developed as a high performance, low latency Si photonics platform for optical engine applications

It reportedly will allow TSMC to offer photonics based co-packaged HPC technology platform. TSMC is developing the integration of COUPE and CoWoS in one CPO package to bring the HPC/AI components to a new era in power and performance.

IFTLE will be following these developments closely as they approach commercialization.

For all the latest in Advanced packaging stay linked to IFTLE…………….