Before we take a look at some exciting news from AMD, it’s that time of year to please allow me to wish all of you a very Merry Christmas and Happy new year. As long-time readers know, I always use this time of year to update you on the activities of my granddaughters Hannah and Madeline. We recently got together for Thanksgiving in NYC and in the picture below the girls are shopping in Chelsea. What a difference 10 years makes. Hannah was just admitted early admission to Swarthmore College where she will run track next fall. If I can give you any free holiday advice it would be to enjoy your family while you can because time truly does fly by.

What’s Inside AMD’s Milan-X CPU Die?

At this year’s IEEE 3DIC Conf held on NC State campus, AMD described its new packaging innovations being used in its Milan-X CPU die.

The presentation of Raja Swaminathan, Sr Fellow at AMD, entitled Advanced Packaging: Enabling Moore’s Law’s Next Frontier through Heterogeneous Integration (HI) was certainly one of the best-received presentations of the conference. It was timed to coincide with AMD press announcements on its newly released Milan-X CPUs.

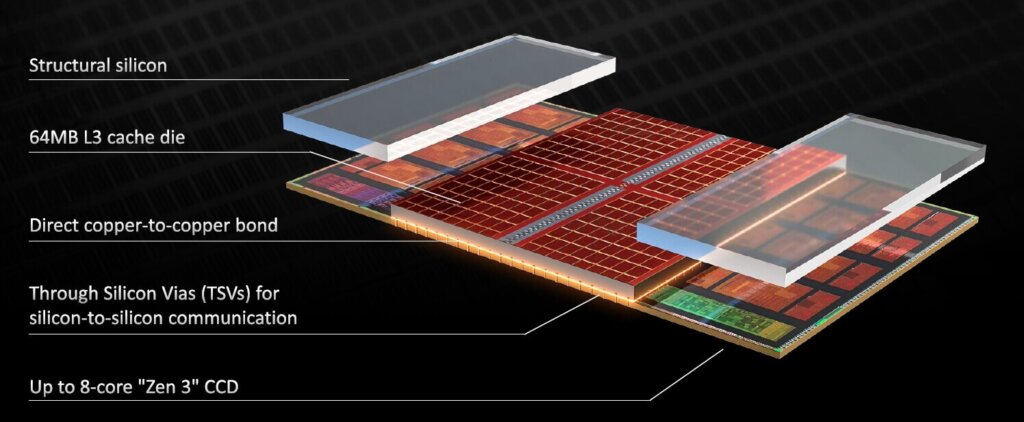

The AMD EPYC Milan CPUs have been based on 7nm Zen 3 architecture. The Zen 3 cores will be fabricated on the TSMC 7nm+ process node. At the 3DIC conference, Swaminathan described AMD’s new third-generation EPYC CPU codenamed Milan-X. It is the company’s first server CPU with 3D chiplet technology. The processors have three times the L3 cache compared to standard Milan processors.

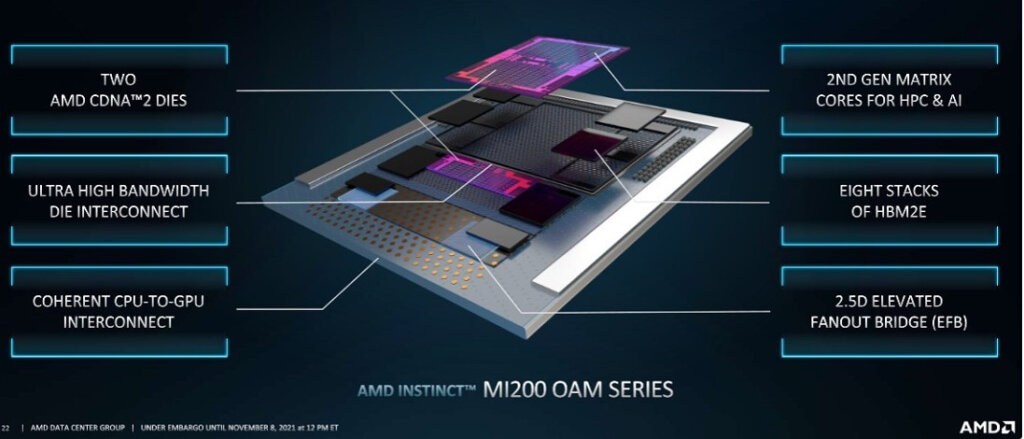

The MI200 is the world’s first multichip GPU, designed to maximize compute and data throughput in a single package (Figure 1). The MI200 series contains two CDNA 2 GPU dies harnessing 58 billion transistors. It features up to 220 compute units and 880 second-generation matrix cores. Eight stacks of HBM2e memory provide a total 128 gigabytes of memory at 3.2 TB/s, four times more capacity, and 2.7 times more bandwidth than the MI100. Connecting the two CDNA2 dies are Infinity Fabric links running at 25 Gbps for a total of 400 GB/s of bidirectional bandwidth.

Milan-X with 3D V-Cache employs both hybrid bonding and through-silicon vias (TSVs), reportedly providing 200X the interconnect density of 2D chiplets and 15X the density compared to the existing 3D stacking solutions. The L3 cache to Zen 3 die interface uses direct copper-copper hybrid bonding (reportedly at 9um pitch) and the TSVs connect through the Zen 3 die as shown in Figure 2.

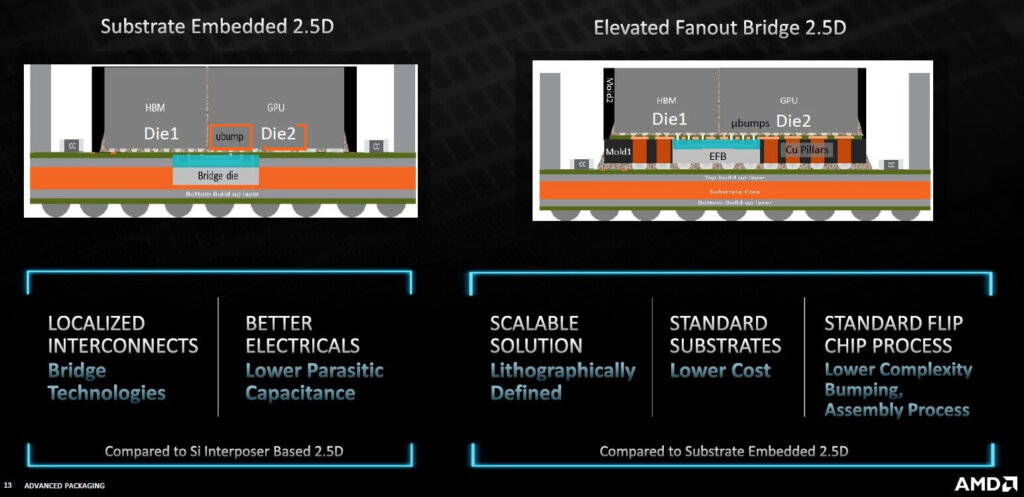

AMD also announced its Elevated Fanout Bridge (EFB) technology (Figure 3). Unlike substrate embedded silicon bridge architectures, EFB reportedly enables the use of standard substrates and assembly techniques, “…providing better precision, scalability, and yields while maintaining high performance.”

Microsoft Azure is the first announced customer for Milan-X. Traditional server partners Dell HPE, Lenovo, and Supermicro are preparing Milan-X products for the first quarter of 2022.

In addition, the MI200 will be powering three giant systems on three continents. In addition to Frontier, expected to be the United States’ first exascale computer coming online next year, the MI200 was selected for the European Union’s pre-exascale LUMI system and Australia’s petascale Setonix system.

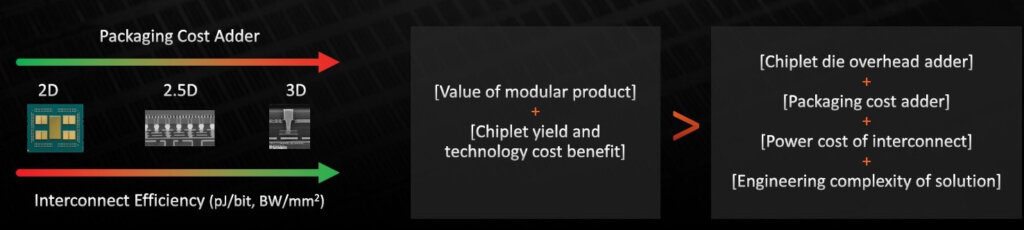

Swaminathan noted that no single packaging architecture works well for all products and that choices are made based on power, performance, area, and cost (Figure 4).

For all the latest on Advanced Packaging stay linked to IFTLE……………………………