Before we start this week’s blog, let me take the opportunity to wish all IFTLE readers a Merry Christmas and Happy New Year. As has been traditional for the past decade-plus, I include a 2019 photo of the granddaughters Hannah and Madeline, who, as you can see, continue to grow up.

Before we start this week’s blog, let me take the opportunity to wish all IFTLE readers a Merry Christmas and Happy New Year. As has been traditional for the past decade-plus, I include a 2019 photo of the granddaughters Hannah and Madeline, who, as you can see, continue to grow up.

You probably have seen that the Heterogeneous Integration Roadmap is now available for public consumption. The charter of the HIR is to provide a long-term vision for the electronics industry, identify difficult future challenges and propose potential solutions. The HIR team attempted to look at the electronics industry’s evolution over the next 15 years and provide a 25year vision for the heterogeneous integration of emerging devices.

It is a volunteer initiative using expert professionals from across the industry, academia, and research institutes for the common good. The HIR is sponsored by three IEEE Societies (Electronics Packaging Society, Electron Devices Society, and Photonics Society), SEMI, and ASME. The HIR team is comprised of 22 Technical Working Groups which represent the electronics ecosystem.

Roadmaps: A Word of Caution

Before we look at the HIR roadmap, IFTLE will offer a word of caution about roadmaps in general. My opinion is that roadmaps should not be used to tell us where we shall be or what we will be doing at any specific point in time, but rather to allow the community to focus directly on what is needed to move forward into the future.

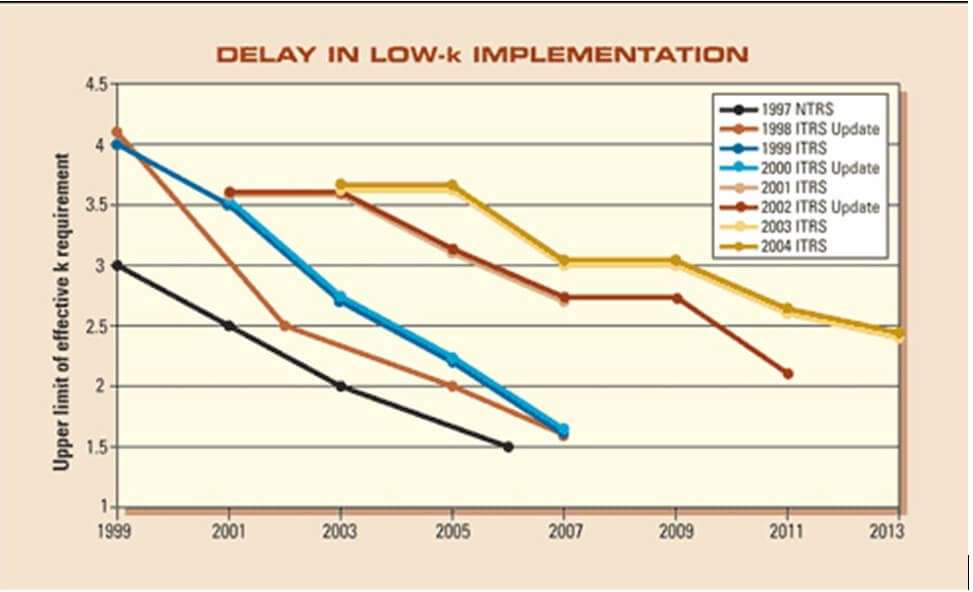

My cautionary example took place in the late 1990s when the industry was focused on lowering the Dk of the interconnect oxide insulation which at the time was basically SiO2. All agreed it would be an easy jump from SiO2 to fluorinated SiO2, which would lower the Dk from ~3.8 to 3.5, but after that, there were many material options, none of which appeared to be a technological given. In 1997 the ITRS assembled all the “industry experts” who subsequently predicted that by 2001 the average Dk would be 2.5.

To make a very long and bloody story short, the Semiconductor International (SI) graph in Figure 1 plots the 1997 roadmap projections vs the next seven years of updates. Notice how they continually adjust the proposed Dk upwards as it became obvious that predictions were not being met. In fact, 20+ years later we have still not achieved a Dk of 2.5. Having lived through that period, my observation as to why the abysmal failure to predict future advances in lowering the Dk is that corporate politics got in the way of scientific evidence as each company tried to outdo their corporate rivals in terms of their “rock solid” projections.

I watched the same thing happen in 2007/2008 when Intel, IBM, and others made marketing announcements that they were ready to implement 3D ICs, when in fact they would be many, many years away from such a move. I’m certainly NOT insinuating that this is a problem with the HIR roadmap, just saying that I learned long ago not to blindly believe politicians, marketing presentations or consensus industry roadmaps. I will say with certainty that I doubt anyone can look 15 to 25 years out and give you an accurate prediction of the future of technology.

Now back to the HIR roadmap…

Heterogeneous integration refers to the integration of separately manufactured components into a higher-level assembly [system in package (SiP)] that, in the aggregate, provides enhanced functionality and improved operating characteristics. The system may be heterogeneous by material, component type, circuit type, node or bonding/interconnect method. In essence, any package with multiple chips in it that are not identical chips is by definition heterogeneous integration.

Heterogeneous integration refers to the integration of separately manufactured components into a higher-level assembly [system in package (SiP)] that, in the aggregate, provides enhanced functionality and improved operating characteristics. The system may be heterogeneous by material, component type, circuit type, node or bonding/interconnect method. In essence, any package with multiple chips in it that are not identical chips is by definition heterogeneous integration.

So, as you can see, this is really not anything new, every module described in the McGraw Hill’s MCM Technology Handbook that we published in 1998 is indeed an example of heterogeneous integration (Figure 2).

HIR members have identified six market application areas that are the leading technology drivers for the HIR roadmap. Namely:

- High-performance computing and data centers

- Medical, health and wearables

- Autonomous automotive

- Mobile

- Aerospace and Defense

- IoT

The building blocks they identified for electronic systems are:

- Single-chip and multi-chip integration

- Integrated photonics

- Integrated power electronics

- MEMS and sensor integration

- 5G, analog, and mixed-signal

In addition, they identified three major technology areas for heterogeneous integration:

- SiP

- 3D and 2D interconnects

- Wafer-level packaging (fan in and fan out)

Much of the roadmap’s 23 chapters do a nice job reviewing the status of current technology, as of 2019, making it a very valuable tool, if only for this one aspect.

From the “single and multi-chip” committee comes the following quote that they reference to Gordon Moore in the late 1960s (again this is an observation NOT A LAW) “It may prove more economical to build large systems out of smaller functions through heterogeneous integration into SiPs, which are separately packaged and interconnected. The availability of large functions, combined with functional design and construction, should allow the manufacturer of large systems to design and construct a considerable variety of equipment both rapidly and economically.”

The aerospace and defense committee defined their market segment as unique because it requires:

- High performance – access to leading nodes and advanced packaging technologies

- High reliability – harsh environments, human safety

- Long product lifecycles – parts obsolescence and upgradability

- Low volumes – high product mix

- A domestic supply chain

The last requirement is especially a problem because they are seeing:

- Foundries concentrated in Asia

- Chinese players growing in importance

- Increasing consolidation among leaders

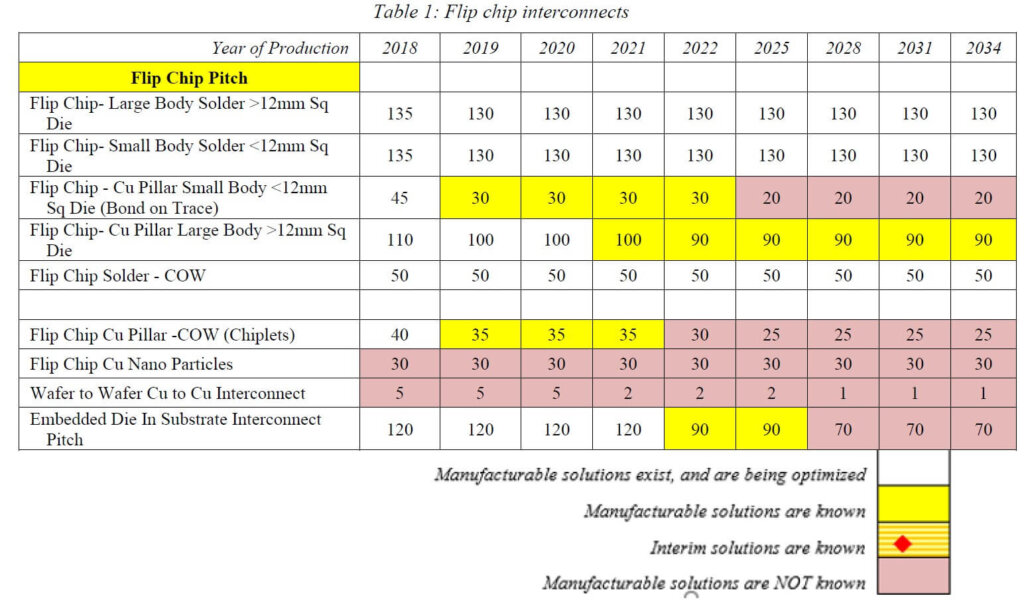

For the most part, HIR projections seem reasonable enough, such as the following bumping roadmap developed by the single and multi-chip group (Figure 3).

Speaking for the industry community, IFTLE would like to thank the participants for the extensive work they put into this effort.

For all the latest in Advanced Packaging stay linked to IFTLE……………………………….