Accomplishment

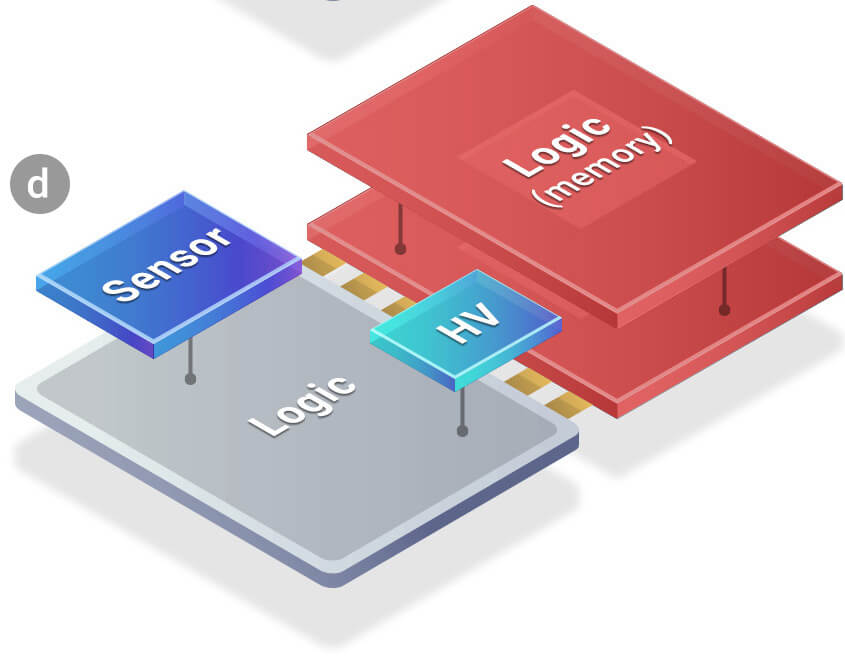

TSMC's bumpless System on Integrated Chip (SoIC™) is a 3D chiplet solution that features ultra-high-density-vertical stacking for high performance, low power, and minimum resistance-inductance-capacitance. SoICs are built using front-end 3D processes and can comprise mixed nodes, actives and passives, III-V materials, and even memory. Dies are stacked on an active interposer with or without TSVs using hybrid bonding. This bumpless approach achieves <10µm bond pad pitch between chips. SoICs can eventually achieve sub-micron density, unlike 3D ICs, which only achieve multi-micron density with C4 or micro-bumps. After dicing, SoICs can be integrated via back-end 3D in InFO or CoWoS packages. It is a drop-in replacement for system-on-chip (SoC).