Accomplishment

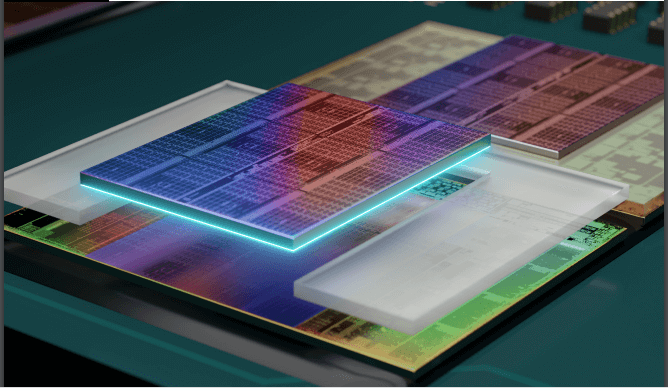

AMD recently released its 3rd generation EPYC processor that implements AMD 3D V-Cache. This is the first true 3D chiplet stacking architecture using the industry’s first copper-to-copper hybrid bonds plus a through-silicon vias (TSVs) approach that provides up to 200 times the interconnect density versus 2D chiplets and approximately 15 times the density versus traditional 3D stacking solutions using solder bumps. The unique bump-less design also consumes less energy than existing 3D approaches. With components placed in a 3D stack for minimum latency, 512increased bandwidth thanks to the tripled L3 cache, and the resultant thermal efficiencies, 3rd Gen AMD EPYC™ processors with AMD 3D V-Cache deliver breakthrough performance, especially for product and engineering design, one of the most compute-intensive workloads.