Accomplishment

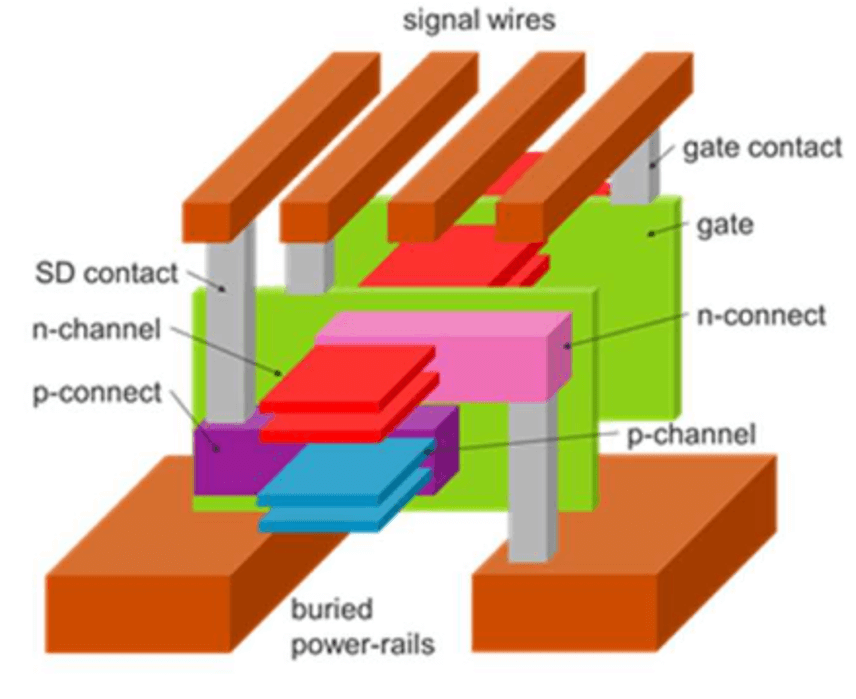

The TEL Tech Center at Albany Nanotech continues to perform leading-edge research on 3D transistor technology and is a key component of both IBM and Samsung transistor development. The center works on both monolithic 3D and heterogeneous schemes and architectures. In this TEL CFET diagram, the main components of a two-transistor (common-gate) CFET device in a 5T cell image with 4 M0 signal tracks. Only two of three channels are shown; n-FET over p-FET stacking follows the stress arguments outlined previously.