3600

Mega DI

Laura Mauer, John Taddei, John Clark, Kenji Nulman Veeco Precision Surface Processing - Horsham, PA 19044 Imauer@veeco.com

Acknowledgements: Kim Pollard and Diane Scheele (Dynaloy) for technical support and guidance using Dynastrip<sup>™</sup> for TSV Clean. John Mucci (CNSE) for assistance in developing TSV Etch recipes for this work.

Dielectric Liner

33% reductio

in RIE Process

Time

Dielectric Liner

## **Effective Post-TSV-DRIE Wet Clean Process for Through Silicon Via Applications**

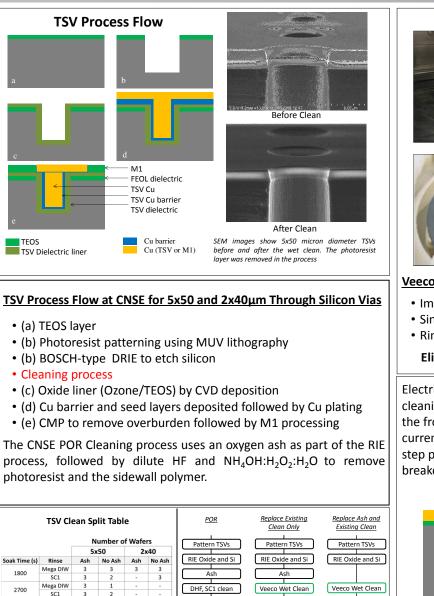

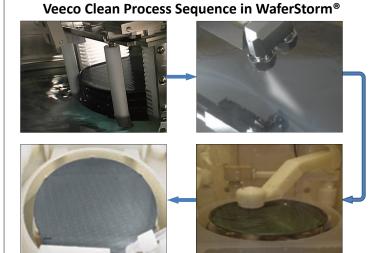

## Veeco Wet Clean Process:

- Immersion batch soak in Dynastrip<sup>™</sup> DL9150

- Single wafer high pressure fan spray with Dynastrip<sup>™</sup> DL9150

- Rinse and spin dry

- Eliminates need for oxygen ash process to strip photoresist

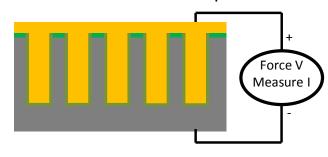

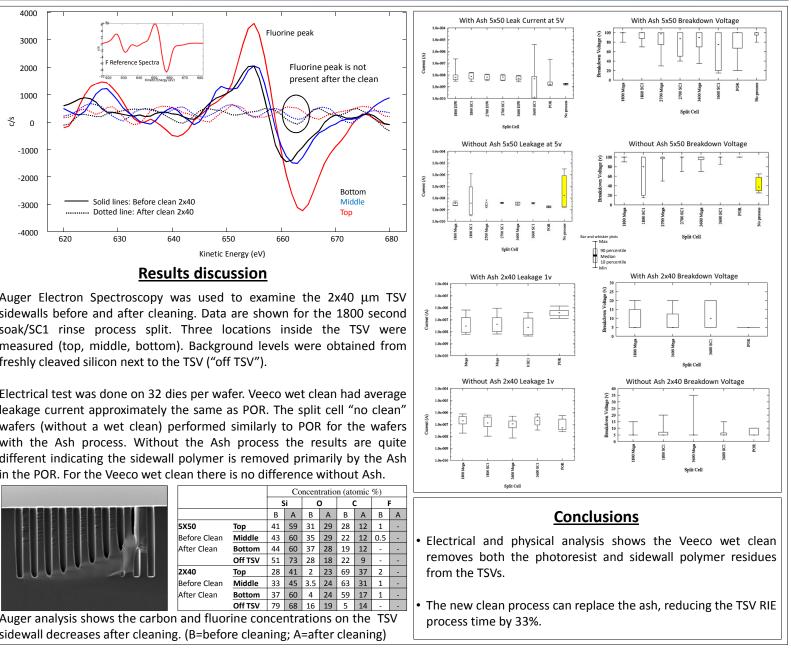

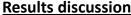

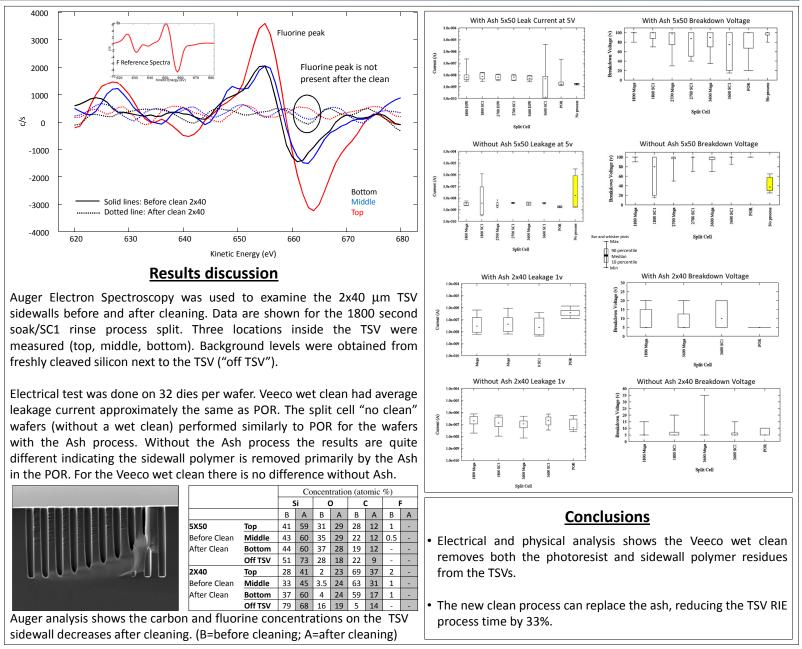

Electrical test was used to evaluate the performance of the cleaning process. Arrays of TSVs are connected to bond pads on the front surface of the wafer. Voltage is applied and leakage current is measured to the substrate. Voltage is then ramped in step pattern to determine voltage where TSV dielectric breakdown occurs. **Electrical Test Setup**

## SUNY POLYTECHNIC

Stephen Olson, Victor Vartanian, Michael Hatzistergos SUNY Polytechnic Institute - Albany, NY 12203 solson@sunypoly.edu