…For while the tired waves, vainly breaking,

Seem here no painful inch to gain,

Far back, through creeks and inlets making,

Comes silent, flooding in, the main….

(Excerpt from Say not the Struggle Naught Availeth, by Arthur Hugh Clough. 1819–1861)

Sitaram Arkalgud, Invensas, quoted this verse to me yesterday over coffee, as we sat discussing the 3D panel he had just moderated as IWLPC 2013 wrapped up its 10th year. It expresses perfectly how it appears the high volume manufacturing (HVM) ramp of 3D ICs will take place. I’ve attended more than my share of keynotes, plenary talks, and 3D focused panels where experts from across the supply chain discuss the readiness of 3D ICs for volume manufacturing. For some time, we’ve heard the same laundry list of challenges that need to be solved before we go to HVM– thermal, test, design tools, thin wafer handling, infrastructure, reliability, cost reduction – but what is becoming clear (at least based on this year’s 3D Thursday plenary talk and 3D panel at IWLPC 2013) is that this list needs to be revamped. Most anyone will tell you that aside from the thermal issues, technologically we’re ready (if we weren’t, would Xilinx be manufacturing products?), that the infrastructure is in place (TSMC, GF, ASE, Amkor all claim to have 300mm 3D TSV lines), and that we can iron out the ‘who-does-what issues”.

This brings us to a revised laundry list with one item on it: cost reduction. As Rajiv Roy of Rudolph Technologies explained, customers are still trying to figure out other ways to get the performance they need based primarily on cost structure. If the device is 90% of the desire performance, they will go with the cheaper alternative. But this Band-Aid approach can only last so long. And guess what? If you’re waiting for through silicon vias (TSVs) to ever cost the same as wire bond products, you’ll be waiting a really long time. As Arkulgud said to me, “we’re not building TSVs to replace wire bonds.” What TSVs really replace is the need to shrink to smaller nodes – and in comparison to that, TSVs offer a cost benefit.

In his plenary talk, This Changes Everything, Invensas’ Simon McElrea drove that point home. McElrea talked about “personal power”, and how we now carry more access to data in our pockets than was needed to put a man on the moon. He also showed how our behaviors and habits have changed due to the smartphone and other mobile devices, such as using our phones to check the time rather than relying on a wristwatch, the way we consume media, and the way we shop. Ultimately, in what McElrea called a “knowledge economy” driven by the Internet of Things (IoT,) we need solutions that give us greater access to data at higher speeds, with lower power consumption, better performance, and increased bandwidth.

McElrea talked about strategic “inflection points” and that 3D IC is the one of these, because its becoming increasingly expensive to produce the next node of technology. Stacking CMOS using TSVs gives us multiple orders of magnitude of power savings, whether you’re talking about mobile battery life or data centers. “3D is ubiquitous. It’s not just a memory solution, it’s a key building block,” explained McElrea. “The OSAT roadmap doesn’t look anything like what it dis 3-5 year ago. It’s a whole different world. We call it Interconnectology.”

During the IWLPC 2013 panel, 3D HVM, Are We There Yet panelist Jim Walker of Gartner, also talked about interconnectology going vertical in 3D and TSV, and how this is driving the future. Ultimately, he said we really have to go 3D on either the chip or the package. And while we’re waiting to see who’s going to jump on the bandwagon first, he offered this paradigm to consider: technology leaders in one wave rarely survive to become the technology leaders of the next (think Wang, Kodak, Digital, and Compaq). Additionally, the leaders who define each wave frequently did not exist in any significant way in the previous wave (think Amazon, Google, Facebook.)

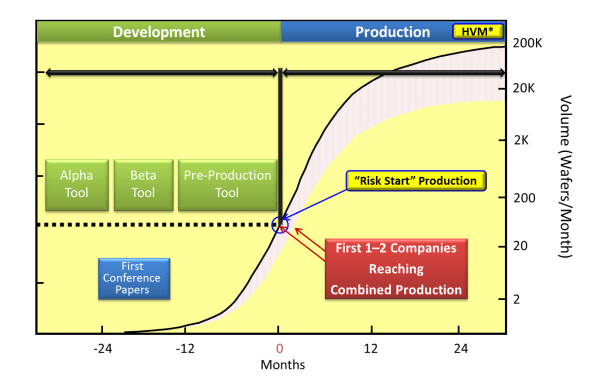

Getting back to the big HVM picture, before we can determine how close we are, we have to understand what HVM means. Arkalgud shared this ITRS Technology Production “Ramp” Curve to demonstrate where 3D IC falls on the spectrum. Based on these parameters, Arkalgud says that with Xilinx’s entire Virtex product family going to 3D, Tezzaron in low volume production of stackable 3D memory, and Micron shipping engineering samples of the Hybrid Memory Cube (HMC), we’ve surpassed the inflection point where development gives way to production. We’re ready to knock down all the barriers and “go all green”, (referring to Xilinx’ Suresh Ramalingam’s slides in his panel presentation.)

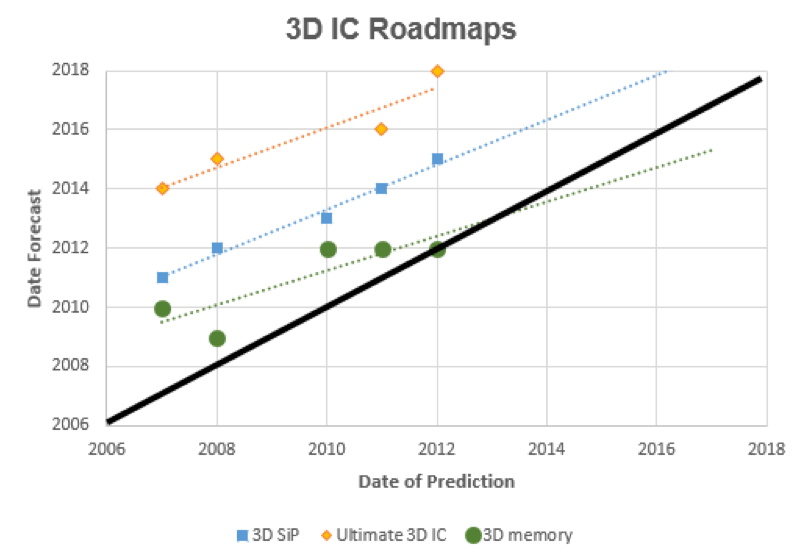

Laura Rothman Mauer, SSEC, talked about how the 3D IC roadmap continues to be pushed out, and by analyzing the various market research roadmaps, she devised her own roadmap by plotting prediction dates in the year they were predicted, and connecting the points to create a trajectory across the real timeline. As you can see, 3D Memory hits the real time line early 2013, which is close to the target if you consider the HMC. 3D SiP and the ultimate 3D IC are at least not on parallel trajectories with the real timeline, but if this is accurate, we won’t be seeing them cross the line any time soon.

After listening to all the reasons why 3D IC production keeps being pushed out for so long, here is my take: when 3D IC reaches HVM has less to do with the manufacturablity of the devices at volume, and more to do with the customers deciding its worth the investment. It’s not that the device can’t be built, its that it can’t be built the cost the customer is willing to pay. When will they willing to pay for it? “When there’s no other way to do it,” predicted Mauer. And if the readiness slides Suresh Ramalingam, Xilinx and Abe Yee, nVidia showed during the panel are anything to go by, that time differs from company to company.

While Xilinx shows the green light in readiness across the board, nVidia is still showing red areas. Mostly, they are waiting for the price to come down. Yee did admit that the company is “willing to pay a little more, but not a lot more” for 3D devices than they do for conventional wire bond or flip chip packages. He also admitted that the next-generation GPU will be a 2.5D interposer, but didn’t say when that would happen. “We’ve been driving Moore’s Law for 10 years, but even if Moore’s Law continues, we’re hitting a bottleneck at the system level because of bandwidth limitations with talking to the memory.” he explained. “We need all the data we can get to crunch information to keep it from stalling… we have to go to a 3D solution on graphics chips, and memory…we need lost of DRAM close by, which calls for real 3D solutions (4-8 stack memory.)”

So its been established: this industry clearly NEEDS 3D to go forward. But it will not come in as a flood but as a trickle that will grow to a steady stream, finally silently flooding the main. ~ F.v.T.