Executive Viewpoint: Inside a Multi-Project Wafer Program for 3D Integration

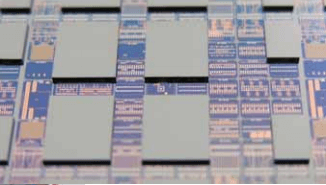

Multi-project wafer (MPW) programs have long been considered an economical way to integrate different IC designs from various teams to produce IC design prototypes and low volumes. Because IC fabrication costs are extremely high, it makes sense to share mask and wafer resources in this way. MPWs were historically used...

Executive Viewpoint: An Interposer Integration and 3D IC Success Story

While the rest of the industry anticipates the coming of 3D ICs, and along with it the long anticipated return on investment that goes with it, one small Silicon Valley fabless has been chugging along, already reaping the benefits of interposer integration and 3D IC technologies. I first heard Farhang...

Executive Interview: Si2 Aims to Boost Confidence in Designing 3D ICs

There’s no doubt left in the minds of semiconductor device manufacturers that the processes required to build interposer-based and 3D IC devices are matured and ready for production. However, the jury is still out in the design community because designing 3D ICs still poses a challenge. Si2 has set out to...

3D By Design: A Blog By and For the 3D Design Community

Earlier this year, I published an open letter to chip and system-level designers regarding 3D integration, suggesting they consider 3D integration technologies as a solution to dealing with the increasing complexity of SoC designs. The post was inspired by my attendance at the Design and Test Europe (DATE 2014) conference,...

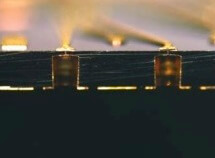

TSV MEOL Process Flow for Mobile 3D IC Stacking

Moore’s law is approaching physical limitations of CMOS scaling, and three dimensional (3D) integration technologies have been proposed as solutions. Wide band transmission between logic and memory is becoming indispensable for not only mobile products, but also other products related to network systems such as servers and data centers. These...

E-System Design: Sphinx 3D Path Finder (“3DPF”) V3.0

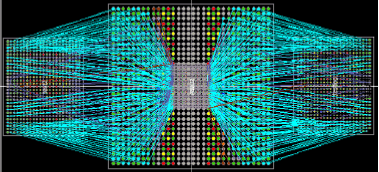

The Sphinx 3D Path Finder (3DPF) is an exploration tool enabling fast test case creation and analysis for silicon and glass interposers containing: solder balls, pillars, bond wires, TSV/TSG as well as RDL interconnect structures. E-System Design: Sphinx 3D Path Finder (“3DPF”) V3.0 All based upon a patented simulation engine with the...

An Open Letter to Chip and System-level Designers Regarding 3D Integration

Dear Chip and System-level Designers, Allow me to introduce myself. My name is Françoise von Trapp, and I am known in the semiconductor industry as “The Queen of 3D”. This is because I have held a deep interest in 3D integration technologies, and have devoted the past 7+ years to...

3D Integration Workshop Faces Reliability Challenges Head On

The Friday 3D Integration Workshop at DATE 2014 once again found me among friends, as an intimate group of about 30 gathered to spend a day sharing knowledge gained since last year’s workshop. My key take-away for the day was how to achieve reliability and robustness. Jürgen Wolf, director of...

Making Progress with 3D IC Design and Test

Thank you, Ann Steffora Mutschler (Semiconductor Engineering) for getting to the bottom of the difference of EDA tools for 2.5D and 3D IC design and test, and providing such a clear explanation in your post, “Evolution vs. Revolution”. In this 2-part post, Mutschler explores the EDA vendor arguments that “tool...

3D IC Design: Outlook for 2014

To date we at Mentor Graphics have seen a handful of 3D IC design releases, and even more customer evaluations. However, the predominant driver seems to be a desire to understand the space in case their company elects to move into the space. In general, the perception seems to be...

2.5D Interposer Innovations from Silex and eSilicon

2.5D interposers sparked a good amount of discussion at this year’s 3D ASIP conference (December 11-13, 2013, Burlingame CA), with a session devoted to “Interposers for all of Us” and other presentations scattered throughout the program to address such issues as thin wafer handling, and heterogeneous integration. Weighing in on...

Part 2: 3D NAND Flash: Towering Spires or Costly Canyons?

In my last blog posting I went over the cost aspects of the Samsung-Toshiba 3D NAND approaches. The conclusion is quite stark: if those vertical holes and trenches are more than a few tenths of a degree from the vertical, then the whole approach can be undercut in cost by...

TSMC 3D IC Reference Flows; A Leap Forward for the HMC

Big news for 3D ICs this week as TSMC and its OIP Ecosystem Partners announce the release of silicon-validated reference flows for both 3D IC stacks and 16nm FinFETS (everyone else puts the 16nm FinFETS first, but I’m most excited about the 3D IC news.) According to Peter Clarke in...

And a Good Time was had by All – 3D InCites Awards Breakfast, 2013

Despite the chilly San Francisco morning temperatures, a sizable crowd of 2.5D and 3D enthusiasts gathered at the Impress Lounge to witness the inaugural 3D InCites Awards Breakfast, held July 11, 2013 during SEMICON West. For me, it was especially significant as it marked four years since I first launched...

Momentum Builds for the 2013 3D InCites Awards

Subscribers are practically blowing up 3D InCites as they duke it out online and race the July 3rd deadline for casting their ballots in the public opinion poll for this inaugural 3D InCites Awards; which is great because the first 3D InCites Awards Breakfast, co-presented by 3D InCites and TechSearch...

Waiting For Godot? Report from D43D 2013, Grenoble, France

Last week, as I have been doing for the last few years, I went to the D43D Workshop. This year, it was hosted by MINATEC in beautiful Grenoble, France. In spite of the severe weather forecast, we had three sunny days with deep blue skies; still snow on the top...

Synopsys: Galaxy Implementation Platform

Product Description Synopsys’ Galaxy™ Implementation Platform is the industry’s leading solution for IC implementation and signoff. Now available with powerful automation for multi-die implementation and foundry certified design flows, Galaxy provides a silicon-proven path to successful implementation of 3D-IC stacked die and silicon-interposer based 2.5D systems. Testimonial Following collaborations with...

Cielution: CielSpot, CielSpot-CTM, CielMech

Product Description CielSpot, CielSpot-CTM and CielMech are thermal and mechanical simulation Software As A Service (SAAS) products based on Cielution’s innovative Cloud based collaboration platform. Users define 3D IC stacking, process and power distribution details at the Cielution online portal to implement complex, but necessary design methodologies with minimal effort....

SavanSys Solutions: 2.5D & 3D Packaging Cost Model

Product Description The 2.5D & 3D Packaging Cost Model is the first tool available to model the total cost and yield from fabrication of the wafers to complete assembly. The user is able to edit a variety of parameters, including TSV and interposer characteristics and die preparation details, and generate...

Apache Design: RedHawk-3DX

Product Description Apache Design’s fourth-generation RedHawk™-3DX simulation software technology extends previous generations’ capabilities to address sub-20 nanometer (nm) designs with 3+ gigahertz performance and billions of gates. It is also architected to support the simulation of emerging chip and packaging technologies using multi-die three-dimensional ICs (3D-ICs) for smart electronic products....