There is a general agreement that chiplet systems are the next step in the evolution of designing dense, complicated, and heterogeneously integrated IC systems. On the one hand, disaggregating monolithic ICs into small ICs provides better cost benefits through better yields and the possibility of mixing technology nodes. On the other hand, it opens up the possibility of integrating specialized chiplets on the same package.

In this context, chiplets look a lot like the hardened IP we are used to dealing with. Today we can seamlessly integrate any hardened IP into a bigger IC. The underlying enabling capability that allows for this to be possible is models – there is a well-defined list of models needed for a hardened IP.

The Chiplet Design eXchange (CDX) is a workstream under the Open Domain Specific Architecture (ODSA) sub-project of the Open Compute Project. CDX focuses on electrical, mechanical, and thermal design exchange standards related to chiplets and chiplet integration in the context of multi-chiplet modules, 2.5D stacked, and 3D integrated circuits (3D-ICs). These enable the foundation for the creation of a market for chiplet systems, modeled after the silicon IP business for single-chip silicon and components business for electronics parts.

The CDX workstream identifies needs and develops guidelines and standards for design automation data models so that chip designers can buy chiplets from third parties and be successful in the high-volume manufacturing of chiplet-based integrated circuits. Participation in this workstream includes players and experts from a cross-section of the semiconductor industry including architects, designers, design automation flows, electronic design automation tool developers, test developers, manufacturers, and assemblers.

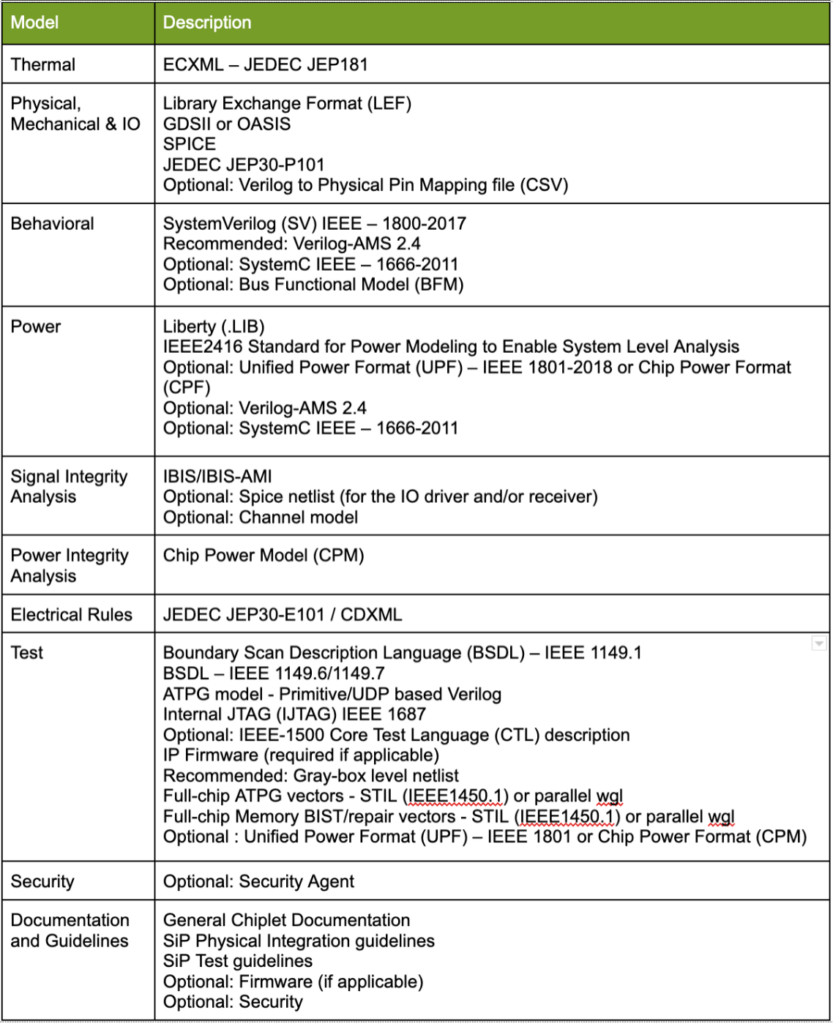

However, integration of chiplets is more complicated and comes with much more consideration than hard IP. Recently, CDX contributed a white paper addressing the need for model standardization for chiplets. It addresses the modeling needed for all aspects of the integration workflow. Table 1 shows a brief list of models addressed in the white paper.

One critical requirement for successful chiplet integration is that all data be presented in machine-readable data format. This allows for automated flows to be built around those models.

For this purpose, CDX adopted CDXML format from a contribution by Palo Alto Electron, which is based on the original ZEF format developed by zGlue Inc. This file captures important information, most of which is typically found in paper datasheets. The file includes mechanical, IO, electrical, assembly, die-to-die, power and thermal, and ESD descriptions.

This file format is a significant contribution that allows for the next generation of automated flows to be built.

Making chiplet integration as seamless and integrating Hard IP into bigger ICs will take some time. The availability of a well-defined set of model requirements is a critical enabling step. Both contributions from CDX are a step in the direction of fully automated workflows.