Part 1 of my DAC 53 reporting focused on this year’s really impressive keynotes, now posted on the DAC website, together with videos of other remarkable pavilion presentations, panels, interviews, demos, etc.….

Part 2 will cover a few highlights that I found very interesting and useful at DAC. Considering that this blog is being posted on 3D InCites, let’s talk about CEA Leti’s 3D network-on-chip (NOC) first. I am quite familiar with their R & D work to increase performance per Watt, reduce form factor, time to market as well as NRE and eventually also lower unit cost. They have contributed 14 pages of in-depth technical information to our latest 500 page Multi-die IC User Guide, now posted on the ESD Alliance’s website for downloading free-of-charge.

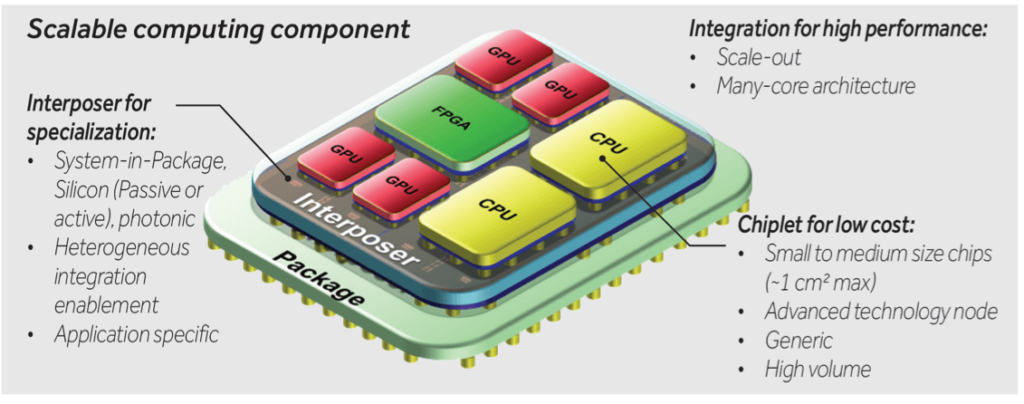

The diagram below shows CEA Leti’s scalable 4x4x2 3D NOC design. It uses a fault tolerant, robust 32 bits asynchronous network on two vertically stacked NOC dies and an interposer to integrate several synchronous die-level IP blocks (a.k.a. chiplets) into the asynchronous network. CEA-Leti showed that the NOC design is fault tolerant; both NOC dies include testability circuits.

If you want more technical details (e.g. floor plan, cross section, functional diagram, performance results,…) about CEA Leti’s 3D NOC and didn’t get a chance to attend their presentation at ISSCC 2016 beginning of this year, you can download the paper, jointly developed with STMicroelectronics and Tima Laboratory in Grenoble, from the IEEE website. The paper’s title is “A 4×4×2 Homogeneous Scalable 3D Network-on-Chip Circuit with 326MFlit/s 0.66pJ/b Robust and Fault-Tolerant Asynchronous 3D Links”.It was presented in SESSION 8 / LOW-POWER DIGITAL CIRCUITS / 8.1.

Vertical stacking of (in this design) only two NOC dies, deploying an ultra-low power asynchronous network and the use of an interposer – instead of a PCB – tells me that optimizing performance per Watt and minimizing form-factor were two important targets for this design and certainly have been met.

Using simple wooden blocks, CEA-Leti even demonstrated at their DAC booth the stacking of the 3D NOC building blocks and the way they are interconnected asynchronously. That’s a fairly compelling way to convey the benefits of using multi-die IC technology to people not yet familiar with the advantages of multi-die ICs.

Actually, I should have mentioned in part 1, that Cadence’ Chuck Alpert, DAC’s MC, used every opportunity to remind the attendees to “Keep Austin Nerdy”. However, Chuck, our Head Nerd, didn’t give us any instructions how to do so. I can only hope that we didn’t give a bad impression to the resident nerds, permanently in Austin.

Anyway, back to business. In addition to walking the exhibition area, getting to know quite a few new companies, catching up with many of my long-term friends and listening to their presentations, I also spent time with team members from my new consulting client, the Electronic System Design Alliance.

Besides the keynotes, described in part 1, I found an IP Panel, moderated by Brian Fuller, now at ARM, very informative. Lisa Minwell from eSilicon, Samsung’s Kelvin Low, Synopsys’ John Koeter and Ranjit Adhikary from Cliosoft addressed: “How do we make IP reuse work?”

Demand for more complex IP blocks at smaller feature sizes is increasing. IP often contain analog and RF functions that need to be verified in silicon; ideally, in exactly the same process technology revision as the final SoC will be using. As IP blocks don’t get reused as many times as years ago, recouping development cost gets more challenging. All these, and most likely many more challenges were implied in the title of this panel and motivated me to attend. My hope to sell panelists and moderator on the idea of combining die-level IP blocks (e.g. memories, analog blocks, RF circuits, MEMS, etc.) on an interposer, all manufactured in their most appropriate process technology, was a bit premature. The discussion showed that technical and business challenges are increasing, but can still be managed by the few remaining IP vendors.

Anyway, if you are working on the bleeding edge of technology, you have to live with disappointment. I plan to raise this subject again at next year’s DAC, June 18 to 22. We’ll meet again in Austin, hopefully, to address more modeling, design ,and verification topics for multi-die ICs, die-package co-design, and system scaling than at this year’s DAC.

Lucky me, I got encouraged to continue pursuing my mission at other conferences. I was able to attend ECTC* the week before DAC and the ASME* conference as well as the MEMS and Sensors Expo* shortly thereafter. These conferences clearly showed that the IC manufacturing community is investing significantly and working hard on cost-effective and reliable building blocks as well as assembly and test solutions for multi-die ICs. The EDA community has still some catching up to do! I look forward to working with both camps to synchronize progress and capabilities of these two very interdependent camps.

Don’t forget to attend SEMICON West in San Francisco from July 11 to 14. This year’s theme “DEFINITELY NOT BUSINESS AS USUAL” and looking at the program will convince you that the only thing constant in our industry is CHANGE. Please face it and act accordingly.

I look forward to addressing multi-die ICs and system scaling again in my SEMICON West blog. Also, I hope YOU will be contributing to the System Scaling Working Group the ESD Alliance will start in Fall 2016. More about this industry-wide effort in a future blog. ~ Herb

*More about these three events also in future blogs.