When Yogi Berra made this very wise statement, he certainly didn’t mean to give specific advice what to choose. I interpret his statement as an encouragement to make an educated decision and pick the best alternative, whenever you come to a fork in the road.

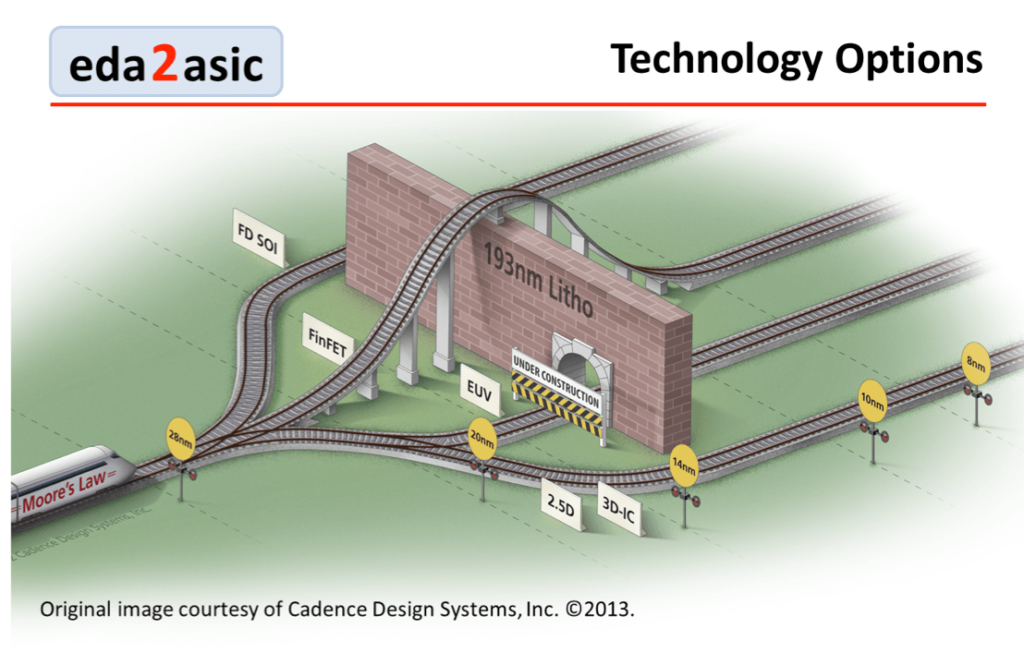

The semiconductor industry is facing such a fork in the road to continued success. As the attached slide from last year’s CDN Live conference expresses, the “Moore’s Law Train” we have been riding for almost 50 years, faces a steep hill. 193nm lithography forces us to use double pattering beyond 28nm, EUV lithography is still not ready for production and excessive leakage in planar transistors requires a switch to FinFETs. These technical challenges make life for IC designers more difficult. In addition, the projected, significantly higher wafer cost causes headaches for purchasing and P&L managers. The discussion about alternatives to feature-size shrinking is in full swing, because more and more people realize that following Moore’s Law may not be the best technical solution or most economical alternative for their applications.

It’s just like buying a new car, unless you have an unlimited budget at your disposal, you need to do some homework, list your requirement and analyze which alternative is technically and economically the best fit. If you are still undecided or want to capture additional information to validate your current technology preference, I recommend my “Technology Update” session next Thursday, April 17, at EDPS* in Monterey, CA. *: EDPS stands for Electronic Design Process Symposium and refers to an annual two day conference where EDA and IC design experts meet to discuss relevant topics for our industry. Here is more about the 21st EDPS conference next week.

Before describing what else EDPS 2014 offers, allow me a few more words about my session: Jamil Kawa, Scientist in Synopsys’ Solutions Group, will present benefits and trade-offs of FinFET technology. I’ll present a brief market update for 2.5D and 3D-IC technology and demonstrate how committed Ansys/Apache, Atrenta, Cadence, Docea Power, E-System Design, Mentor Graphics’ Calibre and Tessent Product Groups, MicroMagic and Synopsys are to supporting 2.5D and 3D-IC design. Last but not least Paul McLellan, SemiWiki blogger and well known EDA expert, will give an update on Fully Depleted SOI (FD-SOI) technology, highlight its technical benefits and talk about the aggressively priced wafers.

If you can’t get away during the day, for our 9 to 5 sessions, please consider joining Mentor’s CEO, Dr. Walden Rhines, for dinner and listen to his keynote: “THE BIG SQUEEZE: Moore’s Law Slowing”. Enjoy the food for thought Dr. Rhines will present and the Monterey Yacht Club’s excellent food for your discerning palate.

Back to other valuable information EDPS 2014 will offer: Our focus all Friday, April 18, will be technical and business aspects of Semiconductor IP. The keynote presentation of Martin Lund, Cadence’ SVP of the IP Division, will start the day. Experts from eSilicon, IPextreme, Arteris, SemiWiki, TSMC, Mentor and Atrenta will present their views of this rapidly growing market and highlight how their companies support customers.

What else is scheduled for Thursday, before the Technology Update session? Chris Lawless, Director System Validation at Intel, will start the day. In his keynote “Going beyond Shift-left for Platform Acceleration with Pre-Silicon SW Solution” he will address pre-silicon prototyping to accelerate time to market. Industry experts from NetApp, Synopsys, Cadence and Altera will address the same subject and share their experience. Early afternoon technology experts from Swan on Chips and Gary Smith EDA, Docea Power, Mentor and Intel will present a range of other Design Flow challenges and discuss solutions.

I hope that this blog raised your interest in the 21st EDPS. Please join us for this informative and highly interactive conference next week and register here. ~ Herb