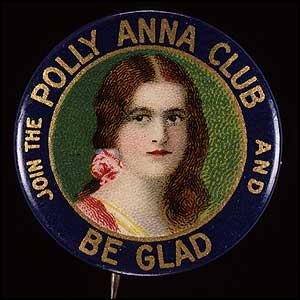

I admit it. I have always been a card-carrying member of the Pollyanna Club. What’s wrong with approaching challenges with optimism? While being realistic about the remaining hurdles to overcome is critical to the 3D IC effort, there’s nothing wrong with a healthy dose of the “Glad Game” to help us keep our eye on the prize.

My good friend and industry colleague, Herb Reiter, recently contributed a blog post to EE TIMES titled SEMICON Showed Support for 3D ICs, in which he relayed detailed feedback from various 3D IC events that took place throughout the week at SEMICON West 2013, and surmised that the supporters are increasing across the supply chain, and investments are being made to solve remaining technical challenges and supply chain issues. We’ve all come to accept that it’s going to be a slow burn to 3D IC commercialization. For many of us, this was uplifting and welcome news.

Not so for an EETIMES reader who identifies himself only as “Chipmonk0”. He really ripped into the post, calling it “Pollyannaish” and offered counterpoints to “all this happy talk,” based on a one hour talk he delivered at SEMICON West titled “Roadmap for TSVs and Alternatives from a Technology Perspective” (although I can’t find any presentation with that particular title on the SEMICON West 2013 website, which might be why Herb and I both missed it.) Regardless, he enumerated a laundry list of negative points, lashing out and taking pot-shots at: Xilinx for “poorly yielding FPGAs”; the blogosphere in general for not reporting the “down in the mud” yields of Samsung’s Wide I/O DRAM; and “slow-poke Govt. funded Euro Labs”. If you’re interested in reading his diatribe you can find it in its entirety here. His “moral of the story” was this: “Give TSVs a fair chance, they need a respite from these overly enthusiastic bloggers, embarrassingly out of their depth, and at conferences lets not blather about supply chain issues, the technical problems are not all solved yet.”

Despite the condescending tone of his comments, the valid points Chipmonk0 had to make were not completely lost on this over-enthusiastic blogger who is admittedly often out of her depth. I just ask him to please note, that some of the previously undisclosed issues he pointed out have gone un-reported due to the fact that companies’ technology failures are not generally shared with the media. As he said himself in one comment that “due to business reasons” he couldn’t go on record.

I would also have to disagree with Chipmonk0’s implication that we are wasting time on supply chain issues. System Level Design’s Barbara Jorgensen and Ed Sperling posted an in-depth story on the supply chain issue titled: 3D IC Supply Chain: Still Under Construction, that begs to differ. The general gist is that most think the technology kinks will be worked out before the supply chain/business model issues, and that the supply chain IS the sticking point. Based on the opinions of those interviewed for the story (Herb Reiter, EDA2asic; Javier DeLaCruz, eSilicon; Kurt Shuler, Arteris; and Frank Ferro, Sonics) in 3D stacks, particularly heterogeneous (for example, Wide I/O on Logic) ownership gets fuzzy, and determining responsibility for finances and design is difficult. But there are ways around that, and many are voting for open collaboration (GLOBALFOUNDRIES’ Foundry 2.0 concept) where everyone invests, and works together (Fabs, Fabless, OSATS) to determine manufacturing process flows. And lets not forget the power-wielding end-customer, who, lets face it, at the end of the day will cast the deciding vote.

On the even brighter side, even if 3D ICs still have technology kinks and cost issues to be worked out, most people agree that working them out will be worth the effort. The reward? As Sperling phrased it, is “high levels of integration, a tiny footprint, energy conservation and blinding speed.”

For example, in a recent blog post, Cadence’s Brian Fuller reports on a presentation titled, Circuit Design Trends: 3D-ICs Extend Scaling given at the Cadence theater in July by Paul Franzon, engineering professor at North Carolina State and well-known 3D IC expert. He says Franzon talked about exponential scaling being enabled by “technologies that are ancillary to CMOS transistors” as well as better circuit design. He gave an example of energy usage, explaining that currently, data storage and communications uses more power than processing, and that essentially it takes more power to take information off the chip than it does to compute the information, and that the reverse is true when 3D ICs are used. He also said that 2.5D interposer technologies afford a 2x power efficiency, and that 3D ICs offer 8x improvement. “Interposers are going to serve quite a useful purpose for a while. But 3D-IC with TSV has a significant fundamental long-term advantage that we’ll be exploiting for quite a while,” said Franzon.

3D ICs have always been the target of much debate. But after all the progress made in 3D IC technology development, I’m still surprised to see that doubters still exist, and their opposition can even seem downright aggressive. With all the clear technology advantages to be gained from commercialization, I find myself wondering why anyone would not be a supporter, unless of course, they think they have a better idea. ~F.v.T